请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TDA4AEN-Q1工具/软件:

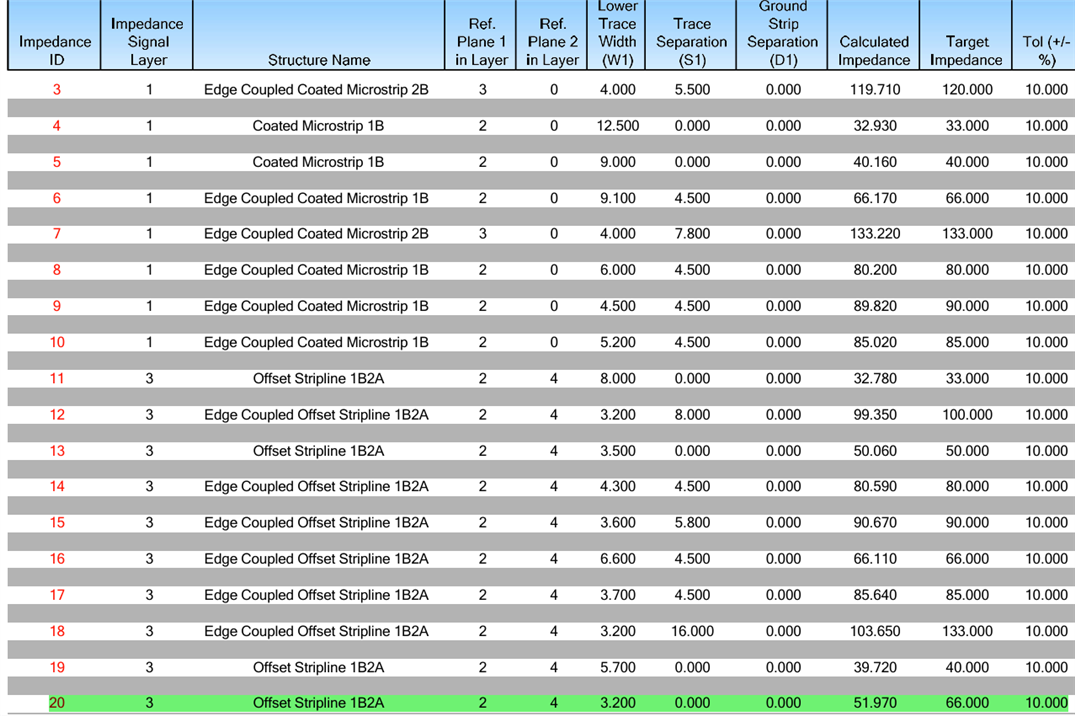

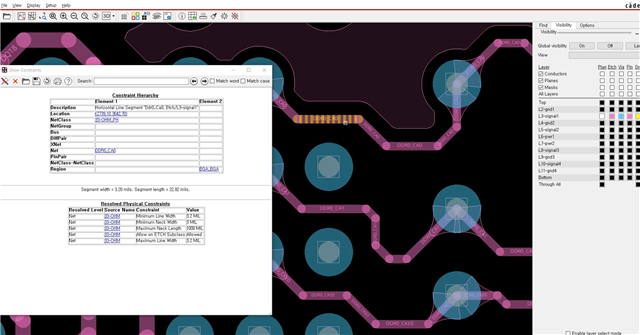

在提供的 EVM 材料中、PCB 指南指示在 DDR T 分支之后维护 66Ω 以获得阻抗。 您能否证实我们是否应按原样遵循这一准则? 附件显示的是 33Ω、因此我们想进行澄清。

在每个堆叠中、Impedance ID 20 显示 66Ω 的第 3 层目标宽度为 3.2mil、而计算值为 51.97Ω。该设置是否为 51.97Ω、因为 66Ω 在 3.2mil 下不可行? 此外、在我们这边是否可以接受以大约 50Ω 进行下一步操作?