工具/软件:

尊敬的 Exparts:

我们的 AM6442 原型板具有一些以太网端口、由 SoC 的 PRU ICSSG 和 DP83867 PHY 组成。

我们需要按如下方式配置内部延迟:

- Rx 内部延迟:2 ns

- Tx 内部延迟:250 ps.

但是、我们在 设置以太网 PHY 的这些设置时遇到问题、想了解配置过程。

1.问题

-忽略 RX 延迟设置。

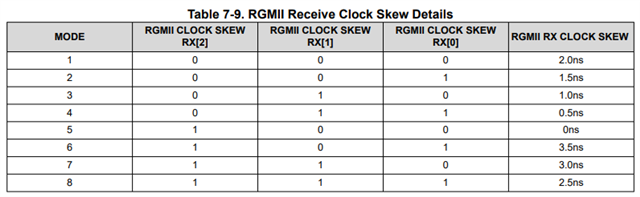

据说是“具有 TX 延迟的 RGMII 模式(在 DTS 中配置)。 RX 延迟不受支持、必须由 PHY 提供。“ 其中

AM6442 原型配置

-使用适用于 AM64X 09_00_03 的 Processor SDK Linux。

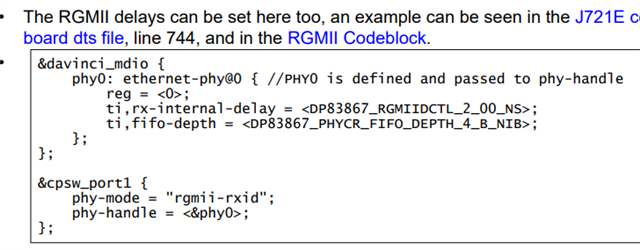

-我们尝试使用如下 DTS 应用以太网内部延迟设置:

/* some configs */

&icssg0_mdio {

/* some configs */

icssg0_phy2: ethernet-phy@2 {

/* some configs */

reg = <2>;

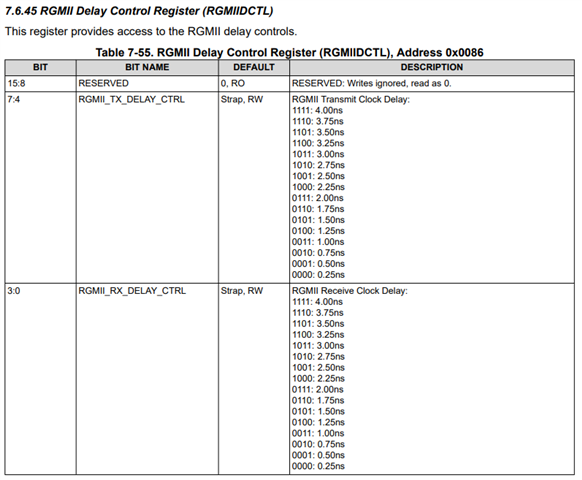

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

/* some configs */

};

icssg0_phy3: ethernet-phy@3 {

/* some configs */

reg = <3>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,tx-internal-delay = <DP83867_RGMIIDCTL_250_PS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

/* some configs */

};

/* some configs */

};

/* some configs */

3.我们想问:

- PRU_ICSSG 与 DP83867 PHY 之间以太网 PHY 内部延迟的具体配置方法。

我们知道 PRU-ICSS 手册 3.6.3.3 中描述了配置限制。 PRU_ICSSG 以太网 — Processor SDK AM64X 文档:“RGMII 模式及 TX 延迟(在 DTS 中配置)“。 RX 延迟不受支持、必须由 PHY 提供。“

您能否解释一下如何进行相应的配置?

此致、

ITO