工具/软件:

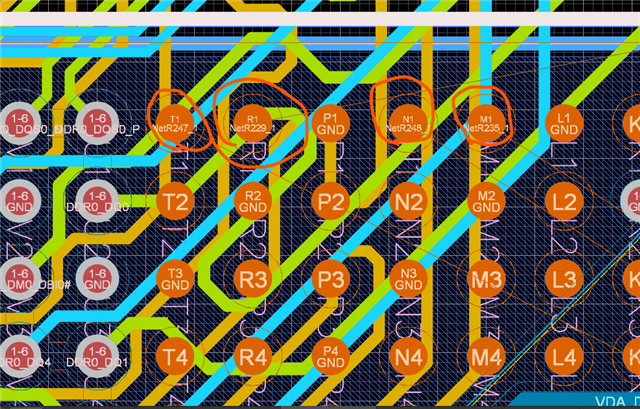

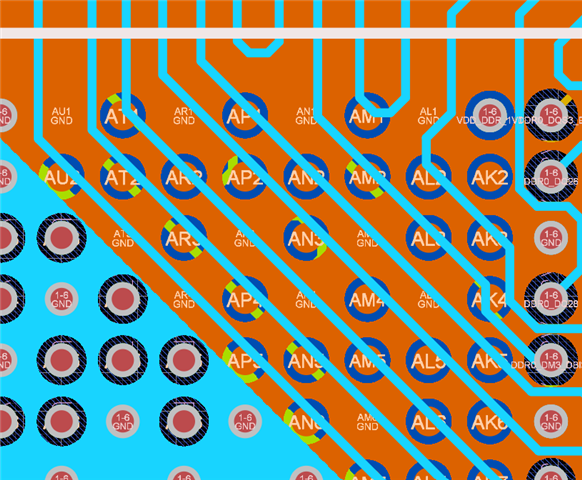

我需要将某些焊盘连接到 VSS VCC/GND、以便在顶部形成一个完整的实心参考平面、因为第二层用作高速信号。

我知道您不应将处理器的某些焊盘/焊球直接连接到 VSS /GND、因为这可能会导致电流浪涌。 因此、建议改为添加下拉电阻以保护 IO。

根据“ 5.4 引脚连接要求 AM69 处理器的数据表中找到。 我们可以在这里找到以下内容:

- 某些引脚必须直接连接到连接到 VSS /GND 的任意下拉电阻(如果未使用)。

- 某些引脚必须直接连接到连接到 VSS /GND 的适当下拉电阻(如果未使用)。

- 如果未使用、某些引脚可以直接连接到 VSS /GND。

- 某些引脚必须直接连接到特定 VCC(如果未使用)的任意上拉电阻器。

但是、如果我移除电源该怎么办? 首先、我不需要 DDR1 到 DDR3。 为何不移除使电流流向 DDR1 至 DDR3 处理器的 0 欧姆电阻器? 我只需要 DDR0。

与某些串行器/解串器相同、所有 CSI、DSI 和 MMC0。 由于 SD 卡、我只需要 MMC1。

那么、如果我“拔下“ AM69 特定外设的电源、会发生什么情况?

- 处理器仍然会启动吗?

- 引脚是否没有电压? 例如、like...no 与任何内容相连?

- 它是否会禁用 外设并且不会发生问题?

我之所以问这个问题、是因为我没有找到任何有关如何 在处理器初始启动时禁用外设的信息。 目标是在不使用 DDR1 时将整个 VSS 直接连接到 DDR1/GND。

有关 PDN、请参阅 SK-AM69 参考原理图。