主题中讨论的其他器件:TMS320F28335、

工具/软件:

尊敬的 TI 专家:

我们正在开发 AM3352(ARM、作为 SPI 主器件)和 TMS320F28335(DSP、作为 SPI 从器件)之间的 SPI 通信链路。

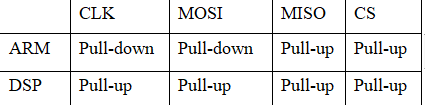

所有 SPI 信号线路上拉和下拉设置仅使用每个芯片的内部配置;电路板上没有外部电阻器。

1.当前配置

• SPI 主器件:AM3352、从器件:F28335

•典型 SPI 速度:1.5MHz

•所有上拉/下拉:仅限内部(无外部电阻)

2.问题

•对于 ARM 主器件到 DSP 从器件的连接、这种上拉/下拉配置是否正确且稳健?

•TI 是否有针对此场景的 SPI 上拉/下拉电阻设置的官方或推荐最佳实践?

•不正确的内部上拉/下拉设置是否会导致数据错位或通信问题、尤其是在上电时?

•是否应该以不同的方式配置任何线路(例如未使用的引脚)?

3.问题

•在此设置中、我们偶尔会看到数据错位或通电后通信中断。

•我们需要确保两侧的上拉/下拉设置均正确。

如有任何官方指导或参考原理图、将不胜感激。

感谢您的支持!

此致、

[周/康尼]