主题中讨论的其他器件:TMS320F28335、

工具/软件:

尊敬的、先生

我是中国南京康尼电子有限公司的工程师。我们发现在使用 AM3352 和 TMS320F28335 进行 SPI 通信时存在以下问题。

控制板 DSP TMS320F28335 和通信板 AM3352 通过 SPI 电缆插头连接、 ARM 作为主器件、DSP 作为从器件。

在使用工程期间、可能会偶尔会在通电情况下发生 SPI 无法通信、SPI 刷写通信故障或持续存在的通信问题。

AM3352 的 Linux u-boot 是 u-boot-2013.01.01-psp06.00.00.00。

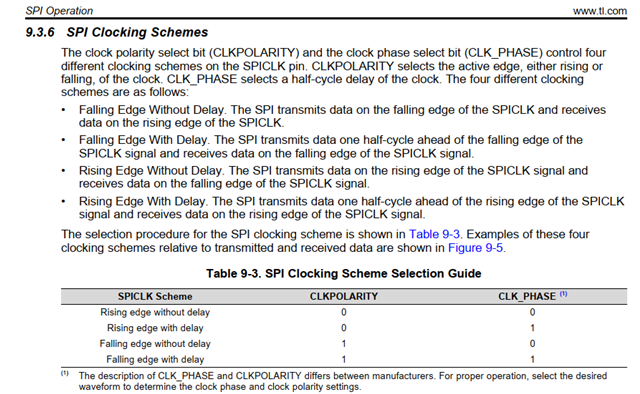

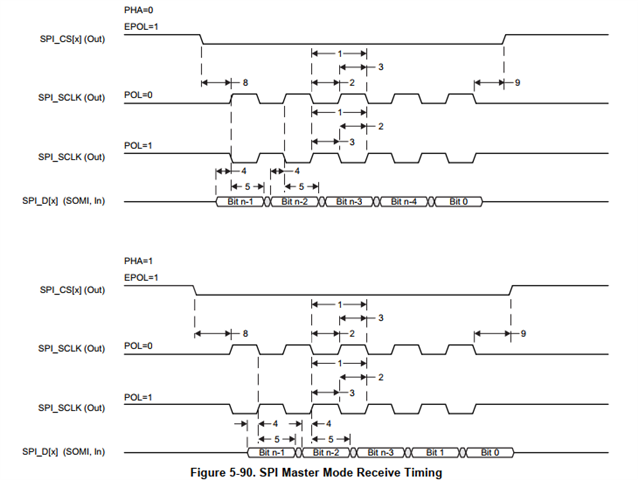

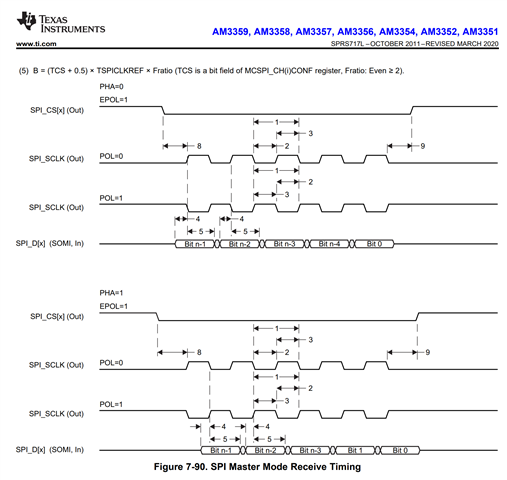

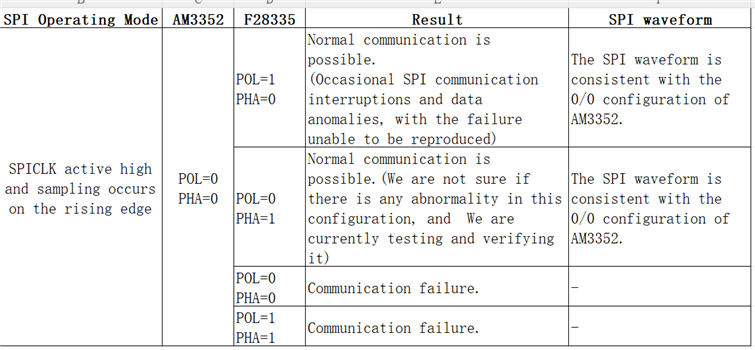

1.为什么在具有相同 SPI 极性/相位配置的 ARM 和 DSP 芯片手册中,数据发送和接收的时钟时序是不同的?

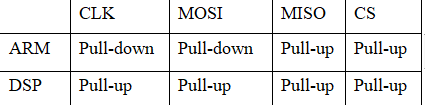

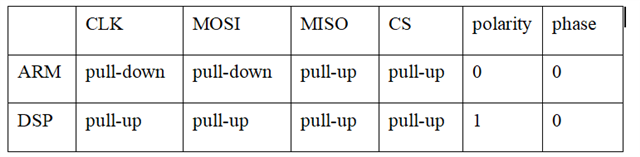

2.当前配置如下,请检查是否正确? 什么是标准配置?

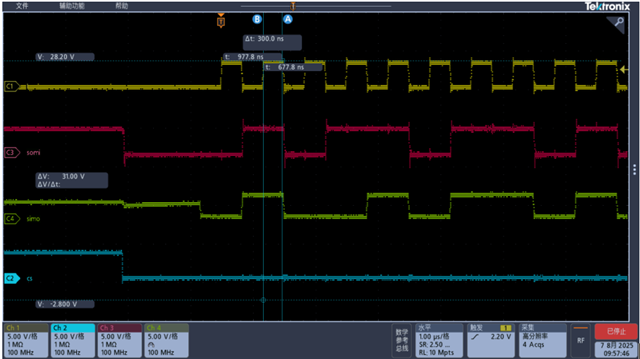

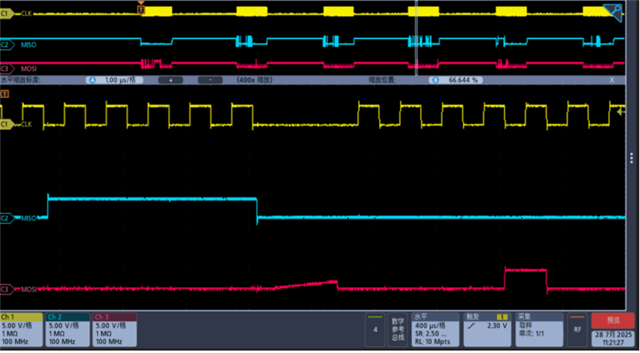

当前配置的 SPI 波形如下。 请检查是否有异常情况? 标准波形是什么?

谢谢!

周