Other Parts Discussed in Thread: SK-AM69, AM69

Thread 中讨论的其他器件: AM69

工具/软件:

这是旧线程的延续、该线程因不活动而被锁定:

SK-AM69:有助于在 SK-AM69 上启用 SERDES/ACSPCIe 输出

你好 藤原拓磨 ,我很抱歉,我没有跟上老线程. 在上一条评论(此处)中、您提到您正在尝试看看是否可以从 SK-AM69 电路板上移除一些电路、看看这是否会在某种程度上产生影响。 我猜在这一点上、你要么没有时间去尝试、要么它没有给你带来什么不同--但是如果你有任何更新、请告诉我。

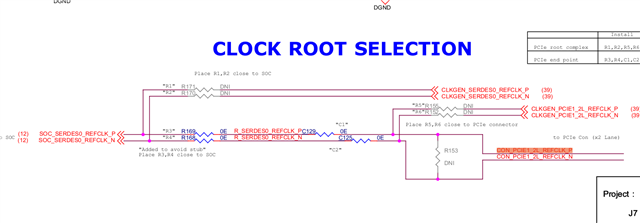

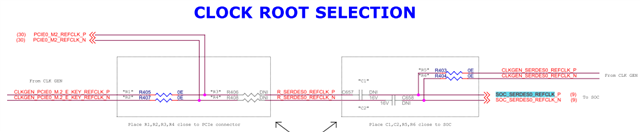

您建议我们可以复制 SK-AM69 通过外部时钟生成电路所做的事情、但由于您提到的 BOM 成本以及它会消耗的 PCB 空间(每一点点位数)、这正是我试图避免的。 因此、我仍在寻找一种方法、让自己确信我们的 AM69 PCB 设计可以在没有额外电路的情况下正常工作。

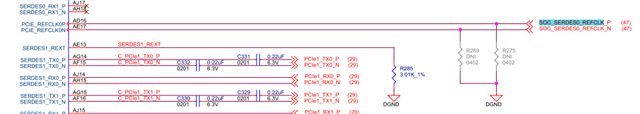

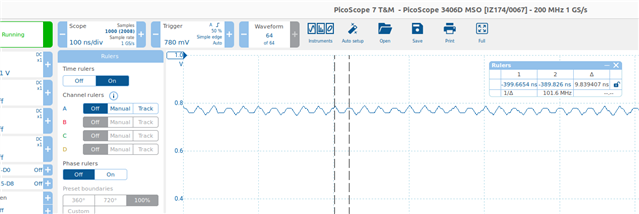

我回顾了我们迄今所做的工作。 根据您在上一条注释中发布的示波器屏幕截图、您似乎能够将 50Ω 终端电阻添加到电路板上、因为我们在执行后都看到 TP106 上~1.8V devmem2 0x118090 w 0x01000002 为了使 PCIe1 的断电位失效。

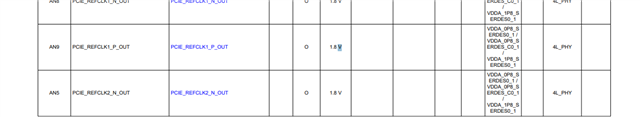

我想、这个 1.8V 电压可能表明 AM69 内部的配置可能错误。 SERDES REFCLK_OUT 引脚(例如连接到 TP106 的 AN9)应为 HCSL(高速电流转向逻辑)、以便输出引脚在驱动 0mA (“低电平时“)和~Ω 14mA (“高电平时“)之间切换。 当该电流通过 50Ω 电阻器传递到接地端时、测试点产生的电压应为 0V(当“低电平“时)或~0.7V(当“高电平“时)。 在我所理解的范围内、HCSL 输出引脚在任何时候都不应该表现出 1.8V 的电压。 根据 TI 对器件的内部了解、在这些引脚上测量 1.8V 是否有意义? SERDES 的误配置是否会导致这种情况发生?

感谢您对此的持续帮助!

此致、

Dave