主题:AM6442 中讨论的其他器件

工具/软件:

评估板在 AM437X_NAND_ADX 线路上没有反反射串联电阻 (22 至 50Ω)、但这是否会导致 EVM 板上的波形出现任何问题?

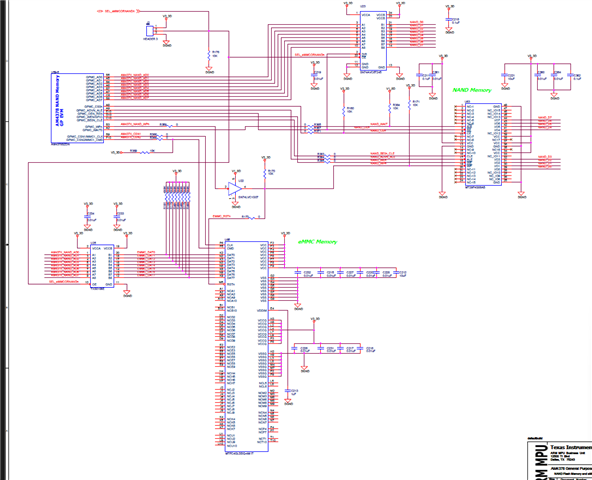

我目前正在通过缓冲器使用 NANDFROM 和 EMMC 来设计电路板、并以此电路作为基准。

我的设计板上 CPU 和缓冲器的图形长度约为 25mm、缓冲器和 NAND 的图形长度约为 20mm。

EMMC 的距离大致相同。 电路板有 8 层、第二层是 GND 平面、可实现阻抗匹配。

我想征求您的意见、认为总线线路上需要串联电阻。