工具/软件:

尊敬的支持团队:

对于一个已持续一段时间的线程、我深表歉意、

但我对以下网站还有其他问题。

客户正在使用单路写入、非多路复用、因此只会执行第一次传输。

在单次写入、非多路复用的情况下、请参考

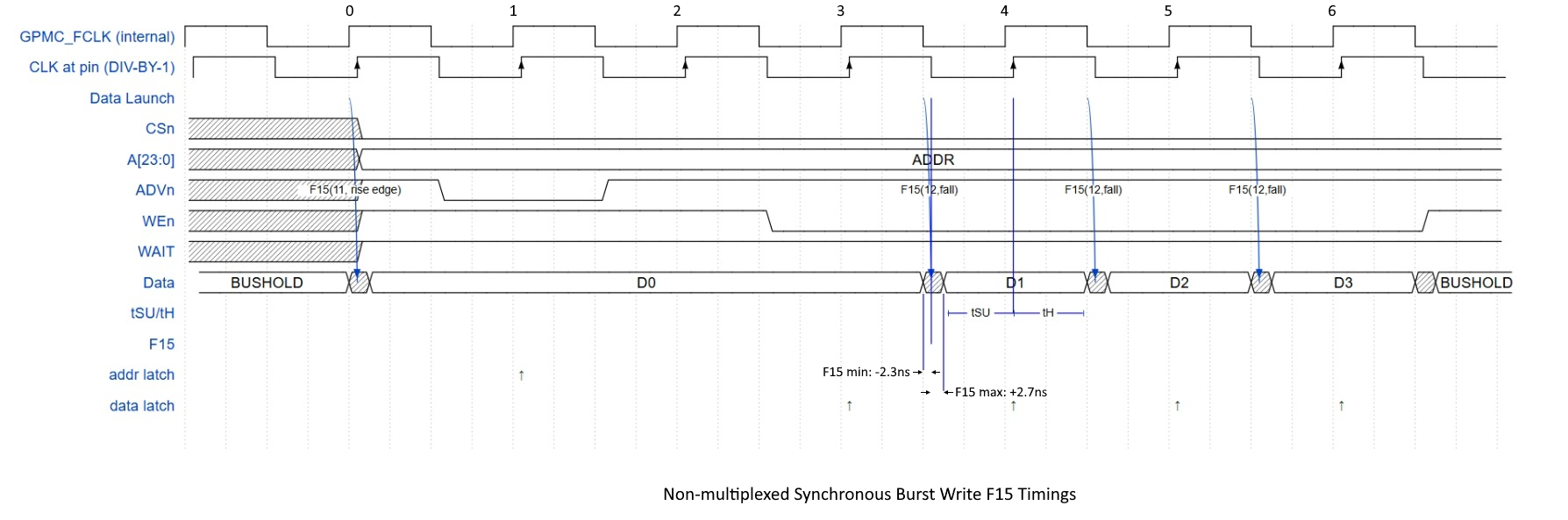

图 6-43. GPMC 和多路复用 NOR 闪存 — 同步突发写入

在数据表中、请告诉我“F15"的“的值是多少。

请确认下面的适当值。

为了澄清问题、图像中的问题如下所示。

问题 1: f15 指定用于转换。 在这里、最小值为 17.7ns、但

最大值为 22.7ns、因此即使在下一个时钟中也无法捕获该数据。

如果为设置指定了该值、我认为 17.7ns 是合理的、但正确吗?

问题 2: f15 指定用于转换。 如果指定了保持、

我认为 22.7ns 对于最大值是合理的、但正确吗?

。

我还想确认的时序图和规格值 进行单次写入和多路复用 结束了。

此致、

Kanae