工具/软件:

您好:

我尝试使用 Jacinto v7.2.0.6 PSDK 将 AUTOSAR 构建应用程序刷写到 MCU2_1。

为 J721E 启动 launch.js 后、我收到以下错误:

MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x18e59ff0 on Page 0 of Length 0x4: (Error -1205 @ 0x18E59FF0) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x410163a4 on Page 0 of Length 0x4: (Error -1205 @ 0x410163A4) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x41c1c214 on Page 0 of Length 0x4: (Error -1205 @ 0x41C1C214) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178)

由于 R5_0 内核点击 main、因此我尝试将二进制文件编程到 MAIN_Cortex_R5_0_1、然后收到额外的错误:

MAIN_Cortex_R5_0_1: Trouble Reading Memory Block at 0x9719e00c on Page 0 of Length 0x4: (Error -1205 @ 0x9719E00C) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MAIN_Cortex_R5_0_1: File Loader: Verification failed: Target failed to read 0x9719E00C MAIN_Cortex_R5_0_1: GEL: File: (...)\StartApplication\Appl\StartApplication.out: Load failed.

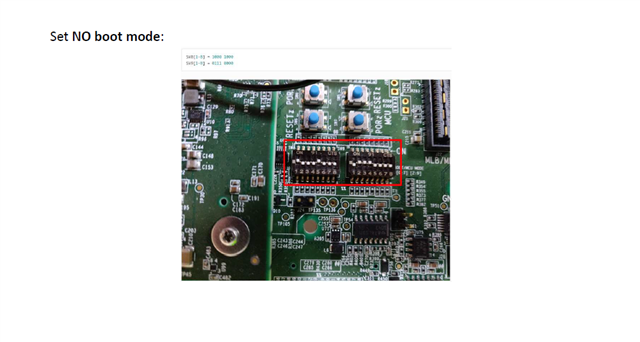

您能支持我调试这个问题吗? 将 BOOT CONFIG 引脚设置为“无引导“:

谢谢、谨致问候、

Tomislav