工具/软件:

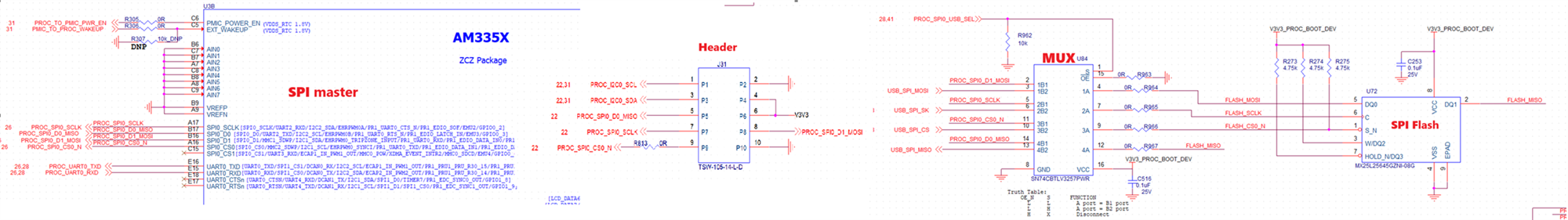

原理图: 主器件为 PROC AM3352 U3、SPI0_CLK 从 PROC 传输到 MUX U84。 多路复用器的输出进入 SPI 从器件 U72。 此 SPI0 总线上还有一个用于测量的接头 J31。 在 PCB 上、布线从 U3->J31->U84。

问题说明:几个主板启动失败。 它总是卡在“启动内核...“。 我们在此电路板上进行了几个实验:

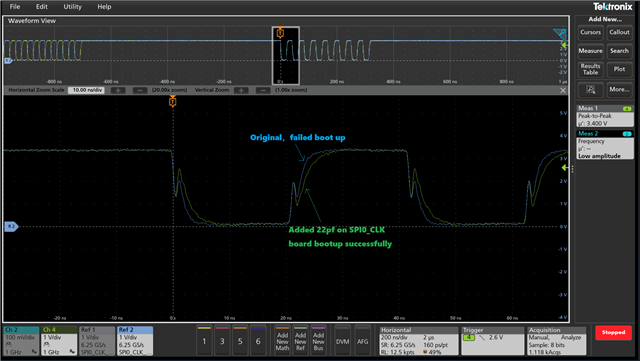

a.在 PROC_SPI0_CLK 上添加 3.6pF 电容器可使电路板成功启动。

b.在 PROC_SPI0_CLK 上添加 1K PD 电阻、该电阻也起作用

c.切断 PROC_SPI0_CLK。 然后插入一个 22 Ω 串联电阻器、即可成功启动电路板。

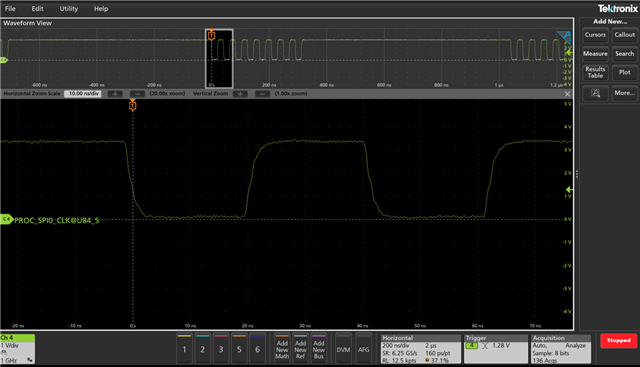

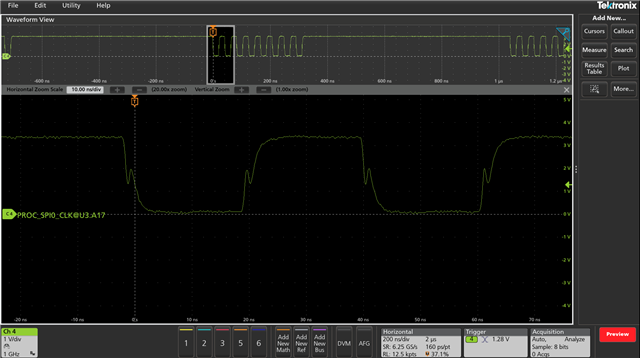

开始时、我们怀疑 PROC_SPI0_CLK 上是否存在较大的过冲、因此我们在目标(U84.5 引脚)上测量了该网络、波形很完美、无过冲、无下冲。 请参阅下面的波形。

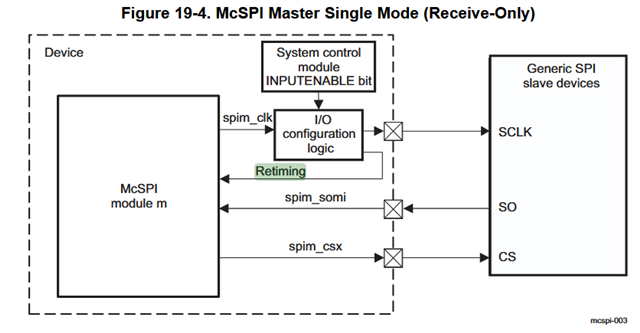

PROC(主器件)侧如何对 MISO 信号进行采样? 它是由 PROC 引脚上的 SPI0_CLK 进行采样、还是在输出触发器之前由 PROC 内部时钟进行采样? 您能否帮助分享 SPI0_CLK 的内部方框图? 我们在源极侧(AM3352 A17 引脚)测量了 PROC_SPI0_CLK。 SPI0_CLK 的上升沿和下降沿存在间隙。 如果在输出引脚上的 SPI0_CLK 上对 MISO 进行采样、则沟道可能会导致问题。

我们正在尝试了解此问题的根本原因。 非常感谢您能为我们提供帮助。