Thread 中讨论的其他器件:TDA4VH

工具/软件:

TDA4VH 定制板

SDK 11.0

FreeRTOS+Linux

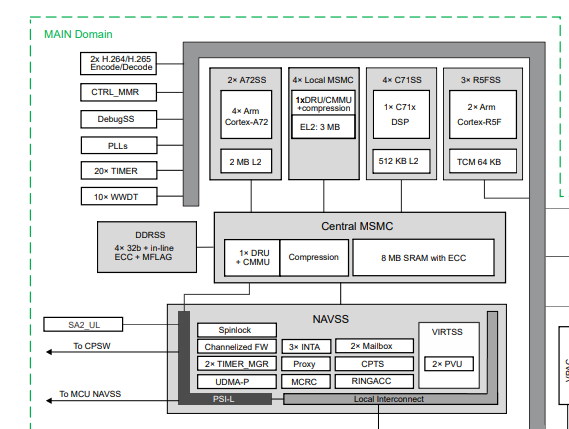

我们在 C7x 的链接器文件中发现了一个 3M 大小的 MSMC 存储器、并了解到应通过 appMemAlloc 函数使用该存储器。

我们想知道此 L3 MSMC MEM 和 L1 L2 MEM 之间有何差异。

2.如果我们要使用它,我们必须使用 appMemAlloc 吗? 否则、它将处于空闲状态吗?

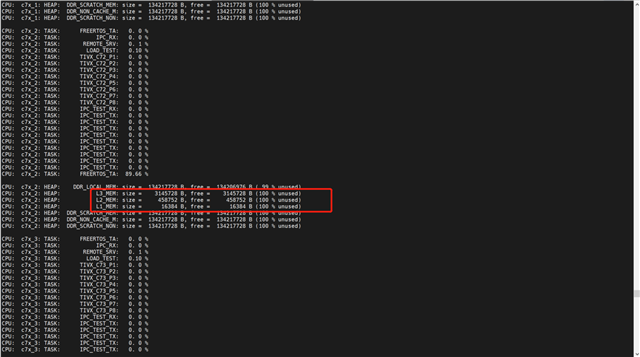

通过使用 perf 接口、我们可以观察到 c7x_2 的 L1_MEM、L2_MEM 和 L3_MEM 均未使用。 这可能是什么原因? 我们是否需要单独配置以启用 L1、L2 和 L3? 还是主动分配存储器?