主题: TPS65910、 TPS82130 中讨论的其他器件

工具/软件:

尊敬的专家:

在对 AM3352 进行电气测量时、发现 AM3352 的 1.1V 电源存在泄漏问题。

经确认、1.8V 电源泄漏至 1.1V_Core 电源。 数据表中的电源序列要求是 1.8V 必须在 1.1V 之前上升。

根据数据表、当 1.8V 电压上升时、1.1V 时会出现轻微的电流泄漏(浪涌)。 此电流泄漏(浪涌)是否有任何影响? 有什么解决方案吗?

谢谢

Daniel

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

在对 AM3352 进行电气测量时、发现 AM3352 的 1.1V 电源存在泄漏问题。

经确认、1.8V 电源泄漏至 1.1V_Core 电源。 数据表中的电源序列要求是 1.8V 必须在 1.1V 之前上升。

根据数据表、当 1.8V 电压上升时、1.1V 时会出现轻微的电流泄漏(浪涌)。 此电流泄漏(浪涌)是否有任何影响? 有什么解决方案吗?

谢谢

Daniel

您好 Daniel、

根据数据表、当 1.8V 电压上升时、1.1V 电压下会出现轻微的电流泄漏(浪涌)。 此电流泄漏(浪涌)是否有任何影响? 是否有任何解决方案?

通过提及 AM3352 数据表的电源一节中提供的 VDD_CORE 附加漏电流注释、我知道当您提到 1.8V 电源时、实际上是指 AM3352 VDDS_RTC 1.8V 电源。 如果情况并非如此、请纠正我、因为我的以下分析认为 VDDS_RTC 是您波形中所示的 1.8V 电源。

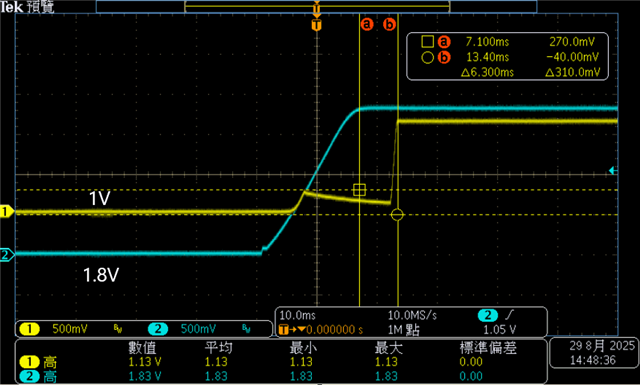

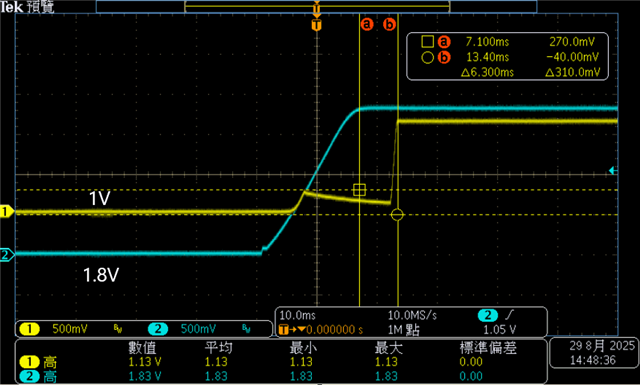

从图 2 中可以看到 VDDS_RTC 的启动时间比 VDD_CORE 早 5ms 左右。 根据注释、当 VDDS_RTC 在 VDD_CORE 之前启动时、VDD_CORE 漏电流不应增加。

以下主题 描述了过去解决的类似问题(观察到的 VDD_CORE 形状非常相似):

上述线程是指以下情况:

SoC 的内部 RTC LDO 被禁用、AM3352 RTC_KALDO_ENn 输入(低电平有效) 连接到 VDDS_RTC。 在本例中、AM3352 CAP_VDD_RTC 引脚用作输入、并 施加来自 VDD_CORE 的 1.1V 电源。

AM3352 数据表中电源时序控制(禁用内部 RTC LDO 时的电源时序控制表下的注释 B 一节介绍了此配置。

综上所述、如果 AM3352 SoC 的 CAP_VDD_RTC 引脚连接到 VDD_CORE、并将 RTC_KALDO_ENn 连接到 VDDS_RTC、则会发生以下情况:

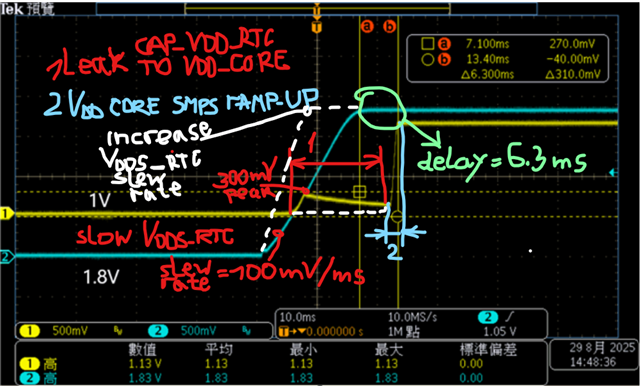

根据波形 2、VDDS_RTC 的上升速度相对缓慢。 在 初始斜升后的 5ms 内、VDDS_RTC 达到 500mV、因此、 当 VDD_CORE 开始上电时、它仍被解释为 RTC_KALDO_ENn 输入的逻辑低电平。 RTC_KALDO_ENn=0 激活 SoC 内部 RTC LDO。 CAP_VDD_RTC 引脚是已启用的内部 LDO 的输出。 由于 CAP_VDD_RTC 在外部连接到 VDD_CORE、因此两个电源之间存在几毫秒的总线争用、直到 RTC_KALDO_ENn = 1 时再次启用引脚 CAP_VDD_RTC 作为输入。

根据上述线程、此类总线争用会导致观察到 VDD_CORE 电源中出现抖动。

借助此类原理图配置、一种可能的解决方案是使用 压摆率更快的 VDDS_RTC — 根据 AM3352 数据表的“电源/小节“电源压摆率要求“一节、建议使用小于 0.1V/us。

请检查您使用的 PMIC 是否在 VDDS_RTC 上未启用软启动。 您是否有在 VDDS_RTC 和 VDD_CORE 之间插入更大延迟的选项?

我希望此主题能帮助您找到解决方案。

此致、

Anastas Yordanov

尊敬的 Daniel:

此现象对 IC 有何实际影响?

当预计在应用 VDD_CORE 的输入处启用瞬态 CAP_VDD_RTC 作为输出时、我需要在内部咨询并与另一位专家确认是否存在与此类瞬态 CAP_VDD_RTC 相关的任何风险。

您提到了如何增加 VDDS_RTC 和 VDD_CORE 之间的延迟。 这种延迟会持续多长时间?

=>您是否有在 VDDS_RTC 和 VDD_CORE 之间插入更大延迟的选项?

我想在之前的分析中我做了一个错误的假设、即 VDD_CORE 更早斜升。 (我将在后续分析中解释。) 在您的波形中、可以看到在 VDDS_RTC 设置为 1.8V 后、VDD_CORE 达到标称值 (1.1V) 约为 6.3ms。 此延迟就足够了。

此致、

Anastas Yordanov

尊敬的 Daniel:

在我之前的分析中、我将 VDD_CORE 的初始 300mV 上升与实际 VDD_CORE 的上升错了。 根据第二个客户波形、实际的 VDD_CORE 斜升(下图中的第 2 级)在 VDDS_RTC 设置为 1.8V 后发生 6.3ms。 因此、我误谈了“激活的“PMIC 的 VDD_CORE SMPS 输出与启用(短暂)的 SoC 内部 LDO CAP_VDD_RTC 输出之间的总线争用。 我提供的线程作为示例:

提供了对 VDD_CORE 的初始 300mV 上升以及随后的沟渠(图中的第 1 级)的以下说明:

“正如 VDDS_RTC 斜升至 1.8V 之前、RTC_KALDO_ENn 处于低电平状态、这意味着 RTC 内部 LDO 已启用、RTC 内部 LDO 是否可以用作电源 (VDDS_RTC? 需要再次确认、如下问题 3) 有流向 CAP_VDD_RTC 引脚的漏电流、然后 CAP_VDD_RTC/VDD_CORE 有小幅斜升、VDDS_RTC 斜升至 1.8V 后 RTC_KALDO_ENn 为高电平 、这意味着 RTC 内部 LDO 被禁用、VDDS_RTC 漏电流被切断、CAP_VDD_RTC/VDD_CORE 出现异常斜升、看起来电源轨出现电平异常、VDD 斜升、

通常、观察到的 VDD_CORE 曲线出现抖动是由于 CAP_VDD_RTC 输出与停用的 PMIC VDD_CORE SMPS 输出之间的瞬态电流泄漏造成的。

根据数据表、当 1.8V 电压上升时、1.1V 电压下会出现轻微的电流泄漏(浪涌)。 此电流泄漏(浪涌)是否有任何影响? 是否有任何解决方案?

应答。 1: 以下是 AM3354 VDD_CORE 异常斜升问题的摘录 、该问题提供了解决方案(据报告不再观察到 VDD_CORE 中的缺口):

“问题现已解决。 这并不是由于上电顺序、客户设计中的上电序列与 TPS65910 完全相同、VDDS 是依次的第一个电源轨。

最后、我们发现它与 TPS82130 的软启动特性相关。 TPS82130 生成的 1.8V 斜升 比慢得多 由于软启动、TPS65910。 一旦 1.8V 电源轨斜升足够快、从 1.8V 到 1.1V 的漏电流似乎就可以消除。 一旦我们禁用了 1.8V DC/DC 的软启动功能、1.1V 上的干扰就会完全消失。“

我怀疑在本例中、压摆率约为 100mV/ms 的 VDDS_RTC 过于缓慢。

同样、您是否可以使用启用了软启动的 PMIC?

应答。 2: 如果能够分析从 VDDS_RTC (1.8V) 到 VDD_CORE (1.1V) 的电流泄漏的影响、您是否可以分享更多详细信息 E2E 私人聊天框中、 如下所示:

1) 使用的电源架构(定义电源序列,电源压摆率,PMIC 配置、RTC 电源配置等)?

2) 至少涵盖所用 PMIC 与 AM3352 SoC 之间相关连接的原理图?

我将重新指派给我们的 TI 电源专家来帮助分析影响。

谢谢

此致、

Anastas Yordanov

您好 Brenda

原理图已通过专用 E2E 消息发送给您。

信号测量表明上电时、复位信号出现浪涌(红圈)。 +1V 是最后一个要激活的电源、即电源序列中的最后一个电源。 下图显示了复位波形。

我后来移除了 BAT54(双二极管)和独立连接的网络:nRST_FE11 和网络:nRST_FE11S、出现了相同的问题。 我怀疑这是由于 AM3352 通电时不受固件控制。 对于此复位行为是否存在任何问题?

谢谢

Daniel

尊敬的 Daniel:

感谢您分享原理图! 我快速了解了电源的实现方式、 这与我们验证的任何内容都不同。 以下是一些注意事项:

谢谢、

Brenda