Thread 中讨论的其他器件:PROCESSOR-SDK-J721S2、TDA4VL-Q1、 TDA4VM

工具/软件:

你(们)好

我们的 PROCESSOR-SDK-J721S2 版本为 pdk_j721s2_10_01_00_25

.症状:

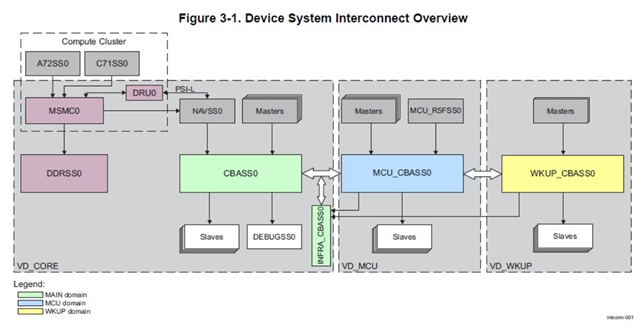

在 主域 (A72/C7x/R5F) 上的大型摄像头/感知负载条件下、MCU_R5F (MCU1_0) 显示抖动和更高的 CPU 负载。

.我们尝试过的:

将确定性代码/数据移动到 MSMC/OCMC/TCM→ 、但我们所有的 MCU 代码太大、一些 MCU 代码 在 DDR 中仍然需要。

μ.申请:

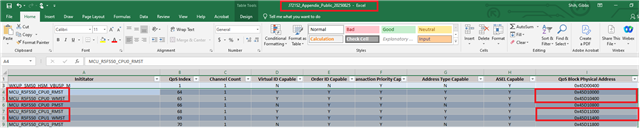

请提供补丁以 在 pdk_j721s2_10_01_00_25 上提高 MCU R5F DDR 访问优先级。

注意:我们了解 QoS 可以提高优先级、但不能保证带宽;目标是在 主域上加载大量摄像头/感知负载时尽可能减少抖动

B.R.

Sanhsin Kuo