工具/软件:

您好、

我想确认是否应将以下要求 (“布线长度“和“对偏斜“)应用于基准时钟。

*www.ti.com/.../spracp4a.pdf

客户将为 PCIe 使用外部基准时钟源 (LP-HCSL)。 我担心的是、他们不仅需要遵循 TX/RX 线路、还需要遵循 REFCLK 的要求。

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我想确认是否应将以下要求 (“布线长度“和“对偏斜“)应用于基准时钟。

*www.ti.com/.../spracp4a.pdf

客户将为 PCIe 使用外部基准时钟源 (LP-HCSL)。 我担心的是、他们不仅需要遵循 TX/RX 线路、还需要遵循 REFCLK 的要求。

此致、

你好、 町田隆一

客户将为 PCIe 使用外部参考时钟源 (LP-HCSL)。 我担心的是、他们不仅需要遵循 TX/RX 线路、还要遵循 REFCLK 要求。

您的理解是正确的。 需要考虑任何 USB3/PCIe 差分对内的延迟差。

https://www.ti.com/lit/an/spracp4a/spracp4a.pdf

此致、

Sreenivasa.

你好、 町田隆一

谢谢你。

您展示的表格适用于“AM64x",“,但、但我的理解是我们可以对 AM67A 应用相同的要求还是正确的吗?

是的。 您还可以看到、包含的 AM65x 信息具有类似的建议。

[报价 userid=“80765" url="“ url="~“~/support/processors-group/processors/f/processors-forum/1568148/am67a-trace-requirement-for-pcie-reference-clock/6056747 ](在本例中,我们应遵循“PCIe 布线长度“和“所有 PCIe RX 对之间的偏差“的规范。)[/报价]不确定所有 PCIe RX 对的含义。

需要考虑任何 USB3/PCIe 差分对内的延迟差。

此致、

Sreenivasa.

您好、

感谢您的答复。

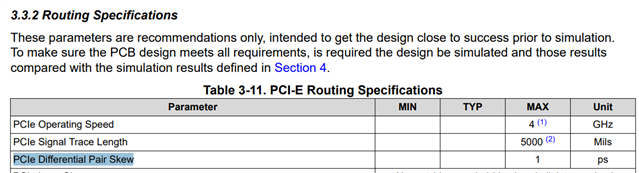

我计算了偏差要求并比较了 www.ti.com/.../spraar7j.pdf 的“表 A-6“ 和 https://www.ti.com/lit/an/spracp4a/spracp4a.pdf 的“表 3-11“之间的规格。

两个结果相似(大约为“1PS")“)、因此我将参考 https://www.ti.com/lit/an/spracp4a/spracp4a.pdf 了解这一点。

此致、

您好、

我来确认一下。

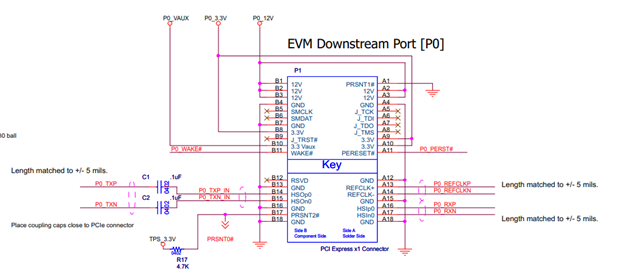

我刚好检查了 EVM PCIe 的参考时钟和 RX 信号的确切长度。

(我选中了 SERDES1_REFCLK_X)

那么、这就是结果。

SERDES1_REFCLK:SOC 的“B16"(“(PCH) 引脚和“B15"(“(Nch) 引脚连接至 CON (J3) 的“A13"(“(PCH) 和“A14"(“(Nch)。

=> PCH 的总长度为“4247.61mil",“,N、N 沟道的总长度为“4226.76mil"</s>“

偏移为 20.85mil。

SERDES1_RX0:SOC 的“C15"(“(PCH) 引脚和“C14"(“(Nch) 引脚连接到 CON (J3) 的“A16"(“(PCH) 和“A17"(“(Nch)。

=> PCH 的总长度为“4296.89mil",“,Nch、Nch 为“4296.58mil"</s>“

偏斜为 0.31mil。

从上面可以看出、RX 信号符合 TI 的要求 (5mil)、但参考 clk 信号不符合 TI 的要求 (5mil)。

我知道用户应该 为参考时钟绘制相同长度的布线、但是您能否重新确认外部 REFCLK 的偏斜要求?

此致、

你好 Ryuuuichi, Machida

请参阅以下内容。

根据下面的信息、我怀疑所有差分对都应该匹配。 (上述 Sitara 处理器应用手册还提到了所有差分对)

https://www.ti.com/lit/an/slla295a/slla295a.pdf

此致、

Sreenivasa.

你好 Ryuuuichi, Machida

有关时钟和信号差分对的长度匹配、请参阅以下建议。 请告知客户、我们预计将遵循以下建议。

使用

PCI Express卡机电规范 3.0 版

2.1.1.低电压摆幅差分时钟

为了减少抖动并允许未来的器件制造工艺更改、这里使用了低电压摆幅差分时钟、如图 2-1 所示。 每个时钟的标称单端摆幅为 0V 至 0.7V、标称频率为 100MHz±300PPM。 时钟在第 4 章中指定的输入阈值区域内具有定义的交叉电压范围和单调边沿。基准时钟对根据最常见的时钟布线规则点对点路由到系统板上的每个连接器。 所有器件的基准时钟分配必须在系统板上的 15 英寸以内匹配。 假设接收器的数据和时钟之间的传输延迟差值小于 12ns。 最大基准时钟不匹配和最大通道长度的组合将产生大约 9-10ns 的值、剩余时间分配给 Tx 和 Rx 器件的插入延迟差值。 在时钟源和连接器之间的任何给定时钟对中、每个信号的布线长度必须良好匹配(< 0.005 英寸)、并与其他非时钟信号适当地间隔、以避免过多串扰。

4.7.7.差分对内的偏移

差分对内的偏斜会产生共模信号分量、进而会增加电磁干扰 (EMI)。 差分对的布线应使差分对内的偏移小于 0.127mm (5mil)(对于附加卡)和 0.254mm (10mil)(对于系统板)。

此致、

Sreenivasa.