工具/软件:

尊敬的 TI 专家:

是用于复位 DDR 电源 (DDR_Reset func)?的步骤

我正在努力解决 SBL 上不同 DDR 的兼容性问题。 使用不同的 DDR 配置编译不同的 SPL 时、执行 memtester 是正常的;通过 SBL 中的 MR 寄存器成功识别不同的 DDR 后、我发现 memtester 会失败。

我还提供了 DDR 兼容性的修改、还请帮助检查它们。

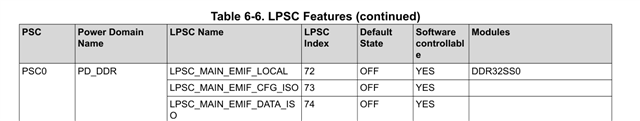

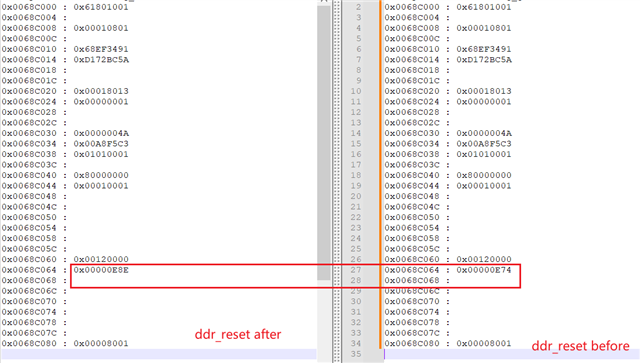

static int32_t ddr_Reset(void)

{

Bootloader_profileAddProfilePoint("Resetting DDRSS 0721——2...\n");

*(volatile unsigned int*)(0x400B20) = (*(volatile unsigned int*)(0x400B20) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B24) = (*(volatile unsigned int*)(0x400B24) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B28) = (*(volatile unsigned int*)(0x400B28) & 0xFFFFFF00) | 0x1;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B20) = (*(volatile unsigned int*)(0x400B20) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B24) = (*(volatile unsigned int*)(0x400B24) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

*(volatile unsigned int*)(0x400B28) = (*(volatile unsigned int*)(0x400B28) & 0xFFFFFF00) | 0x3;

*(volatile unsigned int*)(0x400120) = 0x1;

while(*(volatile unsigned int*)(0x400128) != 0);

return SystemP_SUCCESS;

}

e2e.ti.com/.../0001_2D00_DDR_2D00_2G_2D00_2G_2D00_DDR_2D00_20250704.txt