器件型号: TDA4VL-Q1

要在同一缓存行内共享存储器数据结构、需要执行以下步骤:

1. MCU 1_0 事件触发 ID 为 128 的硬件锁定后、首先执行 cacheInc 的操作、然后写入 a=1 或 2、然后执行 cacheWb 操作以释放 128 硬件锁定

2.在 MCU2_1 周期中、通过 first caching Inc 获得 ID 为 128 的硬件锁、然后写入 b=0、再通过缓存 WB 释放 128 硬件锁

3. a72 核循环访问仅限于 a.

问题描述:

1. MCU1_0 写入 A=1

2. MCU2_1 访问 A=1 确定

3. a72 访问 A=1 确定

4. MCU1_0 写入 A=2

5. MCU2_1 访问 A=2 确定

6. a72 访问 A=1 失败

7. a72 继续访问 A=1 失败

8. MCU2_1 访问 A=2 确定

9. MCU2_1 访问 A=1 失败

10. a72 访问 A=1 失败

11. MCU2_1 访问 A=1 失败

12、MCU1_0 访问 A 也失败 1

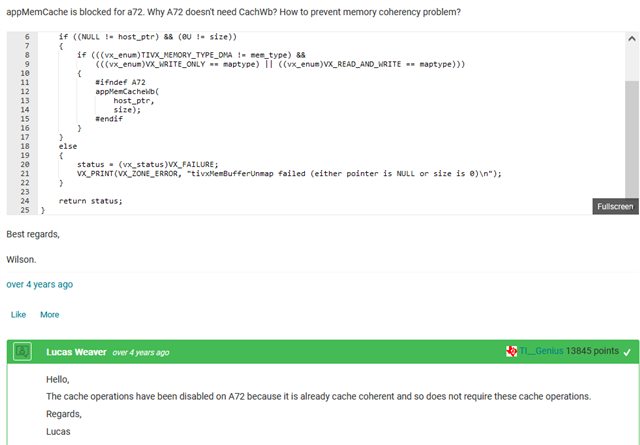

为什么会覆盖为历史数据 1?