Other Parts Discussed in Thread: TPS22965, AM623

器件型号: AM623

主题中讨论的其他器件: TPS22965、

您好:

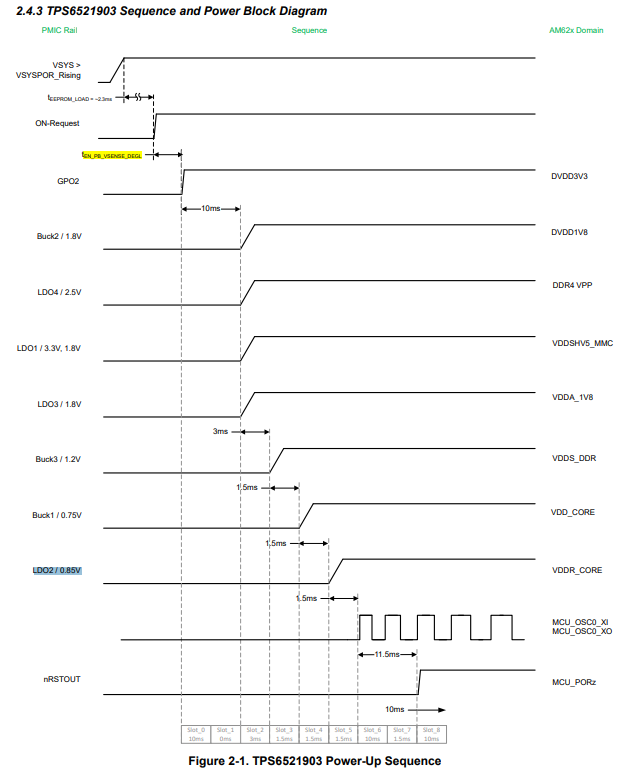

在该参考设计中、PMIC (TPS6521903) 用于对 AM62x 进行电源时序控制并为其供电、如以下 PMIC 文档中所示。

在此上电序列中、第一个由顶部的电源开关 (TPS22965) 提供的 3.3V 电压。 在该参考设计中、该 3.3V 电压用于为 DEV 板上的外设供电、这些外设可以在其余电源上电之前在 AM623 上应用信号或上拉 GPIO 引脚。 这会导致问题吗? 在 VDD_CORE 稳定后、我们是否应该将 3.3V 电源分离为开关为电源外设(包括以太网 PHY)的 3.3V 电源?

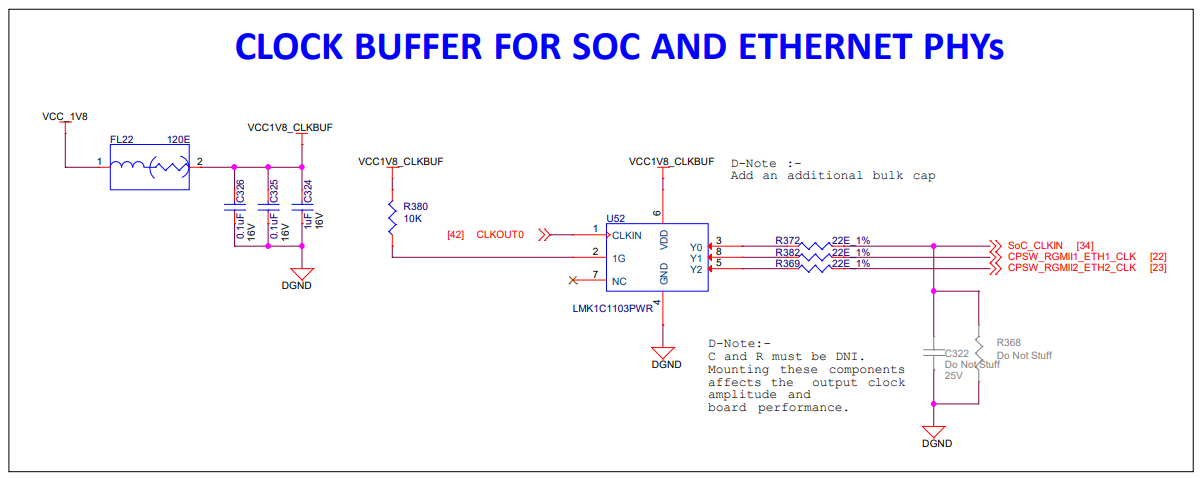

关于该参考设计的第二个问题是针对如下所示的时钟缓冲器使能信号:

如果在下面所示的上电序列中的 LDO2/0.85V 之后启用该时钟、

是否发现在启用 LDO2 之前启用缓冲区的问题? 我们是否应该使用 LDO2 启用时钟缓冲器?