器件型号: AM62A3-Q1

MCAL 插件包含一个邮箱映射部分、用户必须设置该部分。 这些参数有什么含义?它如何实现这些参数?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: AM62A3-Q1

MCAL 插件包含一个邮箱映射部分、用户必须设置该部分。 这些参数有什么含义?它如何实现这些参数?

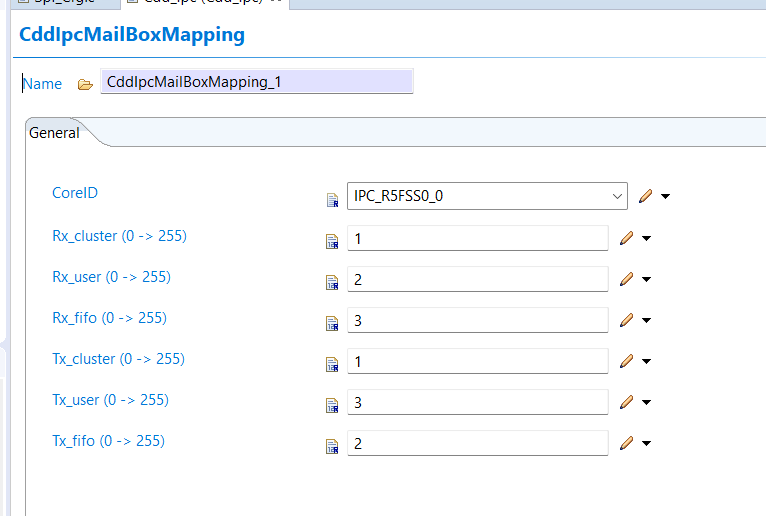

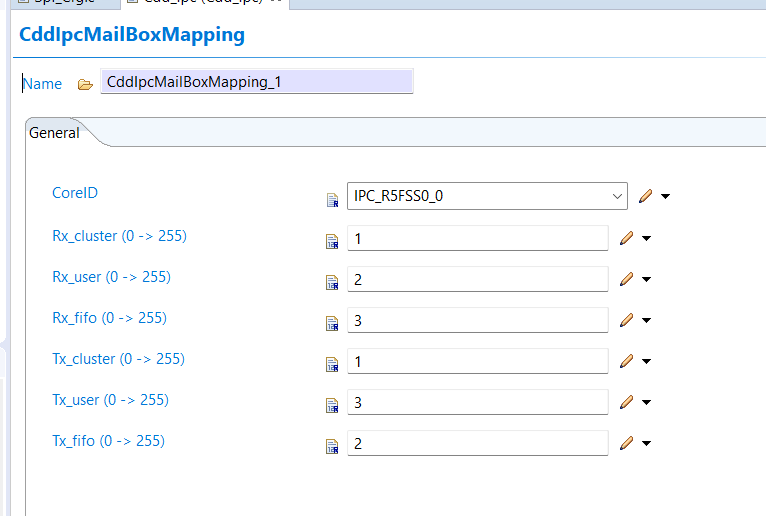

每个 IPC 邮箱配置都包含三个参数:[群集 ID、FIFO ID、用户 ID]

-集群 ID:要使用的邮箱集群/实例(0-7 取决于设备)

- FIFO ID:该集群内的特定硬件 FIFO (0-15)

-用户 ID:目标内核上的接收用户/中断线路

AM62 和 AM275x 器件的邮箱映射如下所示:

AM62X:

- M4FSS0_0 (Cortex-M4F )

- R5FSS0_0 (Cortex-R5F)

- A53SS0_0 (Cortex-A53 内核 0)

From Core | To Core | Cluster ID | FIFO ID | User ID -------------|-------------|------------|---------|-------- M4FSS0_0 | R5FSS0_0 | 0 | 4 | 1 M4FSS0_0 | A53SS0_0 | 0 | 0 | 0 M4FSS0_0 | A53SS0_1 | 0 | 8 | 1 R5FSS0_0 | M4FSS0_0 | 0 | 5 | 2 R5FSS0_0 | A53SS0_0 | 0 | 2 | 0 R5FSS0_0 | A53SS0_1 | 0 | 10 | 1 A53SS0_0 | M4FSS0_0 | 0 | 1 | 2 A53SS0_0 | R5FSS0_0 | 0 | 3 | 1 A53SS0_0 | A53SS0_1 | 0 | 6 | 1

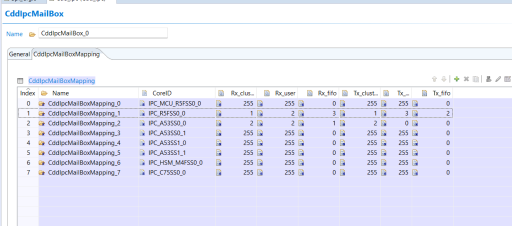

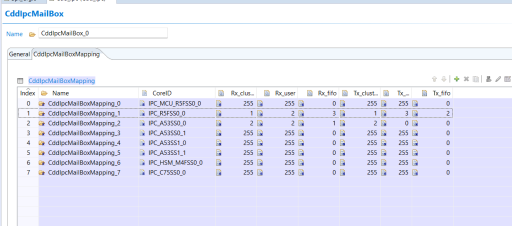

AM62Ax/AM62Dx

- MCU_R5FSS0_0 (MCU 域 R5F)

- R5FSS0_0 (DM R5F — 设备管理器)

- A53SS0_0 (Cortex-A53)

- C75SS0_0 (C7x DSP)

From Core | To Core | Cluster ID | FIFO ID | User ID ----------------|-----------------|------------|---------|-------- MCU_R5FSS0_0 | R5FSS0_0 (DM R5)| 1 | 2 | 3 MCU_R5FSS0_0 | A53SS0_0 | 2 | 0 | 0 MCU_R5FSS0_0 | C75SS0_0 | 0 | 3 | 1 R5FSS0_0 (DM R5)| MCU_R5FSS0_0 | 1 | 3 | 2 R5FSS0_0 (DM R5)| A53SS0_0 | 0 | 0 | 0 R5FSS0_0 (DM R5)| C75SS0_0 | 3 | 1 | 1 A53SS0_0 | MCU_R5FSS0_0 | 2 | 1 | 2 A53SS0_0 | R5FSS0_0 (DM R5)| 0 | 1 | 3 A53SS0_0 | C75SS0_0 | 1 | 1 | 1 C75SS0_0 | MCU_R5FSS0_0 | 0 | 2 | 2 C75SS0_0 | R5FSS0_0 (DM R5)| 3 | 0 | 3 C75SS0_0 | A53SS0_0 | 1 | 0 | 0

AM62Px:

- MCU_R5FSS0_0 (MCU 域 R5F)

- WKUP_R5FSS0_0(唤醒域 R5F)

- A53SS0_0 (Cortex-A53)

From Core | To Core | Cluster ID | FIFO ID | User ID ----------------|-----------------|------------|---------|-------- MCU_R5FSS0_0 | WKUP_R5FSS0_0 | 2 | 0 | 3 MCU_R5FSS0_0 | A53SS0_0 | 1 | 0 | 0 WKUP_R5FSS0_0 | MCU_R5FSS0_0 | 2 | 1 | 2 WKUP_R5FSS0_0 | A53SS0_0 | 0 | 0 | 0 A53SS0_0 | MCU_R5FSS0_0 | 1 | 1 | 2 A53SS0_0 | WKUP_R5FSS0_0 | 0 | 1 | 3

AM275x:

- WKUP_R5FSS0_0(唤醒域 R5F)

- R5FSS0_0 (R5F 集群 0、内核 0)

- R5FSS0_1 (R5F 集群 0、内核 1)

- R5FSS1_0 (R5F 集群 1、内核 0)

- R5FSS1_1 (R5F 集群 1、内核 1)

- C75SS0_0 (C7x DSP 内核 0)

- C75SS1_0 (C7x DSP 内核 1)

From Core | To Core | Cluster ID | FIFO ID | User ID ----------------|---------------|------------|---------|-------- WKUP_R5FSS0_0 | R5FSS0_0 | 1 | 1 | 0 WKUP_R5FSS0_0 | R5FSS0_1 | 2 | 1 | 0 WKUP_R5FSS0_0 | R5FSS1_0 | 1 | 3 | 1 WKUP_R5FSS0_0 | R5FSS1_1 | 2 | 3 | 1 WKUP_R5FSS0_0 | C75SS0_0 | 4 | 3 | 2 WKUP_R5FSS0_0 | C75SS1_0 | 4 | 5 | 3 R5FSS0_0 | WKUP_R5FSS0_0 | 5 | 2 | 0 R5FSS0_0 | R5FSS0_1 | 0 | 2 | 1 R5FSS0_0 | R5FSS1_0 | 0 | 4 | 2 R5FSS0_0 | R5FSS1_1 | 0 | 6 | 3 R5FSS0_0 | C75SS0_0 | 1 | 4 | 2 R5FSS0_0 | C75SS1_0 | 1 | 5 | 3 R5FSS0_1 | WKUP_R5FSS0_0 | 5 | 3 | 0 R5FSS0_1 | R5FSS0_0 | 0 | 0 | 0 R5FSS0_1 | R5FSS1_0 | 0 | 5 | 2 R5FSS0_1 | R5FSS1_1 | 0 | 7 | 3 R5FSS0_1 | C75SS0_0 | 2 | 4 | 2 R5FSS0_1 | C75SS1_0 | 2 | 5 | 3 R5FSS1_0 | WKUP_R5FSS0_0 | 6 | 2 | 0 R5FSS1_0 | R5FSS0_0 | 0 | 1 | 0 R5FSS1_0 | R5FSS0_1 | 0 | 3 | 1 R5FSS1_0 | R5FSS1_1 | 2 | 2 | 1 R5FSS1_0 | C75SS0_0 | 3 | 2 | 2 R5FSS1_0 | C75SS1_0 | 3 | 3 | 3 R5FSS1_1 | WKUP_R5FSS0_0 | 6 | 3 | 0 R5FSS1_1 | R5FSS0_0 | 1 | 0 | 0 R5FSS1_1 | R5FSS0_1 | 2 | 0 | 0 R5FSS1_1 | R5FSS1_0 | 1 | 2 | 1 R5FSS1_1 | C75SS0_0 | 4 | 2 | 2 R5FSS1_1 | C75SS1_0 | 4 | 4 | 3 C75SS0_0 | WKUP_R5FSS0_0 | 7 | 2 | 0 C75SS0_0 | R5FSS0_0 | 3 | 0 | 0 C75SS0_0 | R5FSS0_1 | 3 | 1 | 1 C75SS0_0 | R5FSS1_0 | 4 | 0 | 0 C75SS0_0 | R5FSS1_1 | 4 | 1 | 1 C75SS0_0 | C75SS1_0 | 7 | 1 | 2 C75SS1_0 | WKUP_R5FSS0_0 | 7 | 3 | 0 C75SS1_0 | R5FSS0_0 | 5 | 0 | 1 C75SS1_0 | R5FSS0_1 | 6 | 0 | 1 C75SS1_0 | R5FSS1_0 | 6 | 1 | 2 C75SS1_0 | R5FSS1_1 | 5 | 1 | 2 C75SS1_0 | C75SS0_0 | 7 | 0 | 1

映射表中的每一行显示:

-从核心:发送消息的源核心

-至核心:接收消息的目标核心

-群集 ID:要使用的邮箱群集

- FIFO ID:该群集中的哪个 FIFO

-用户 ID:接收器上的哪个中断线路

示例:如果您看到“MCU_R5FSS0_0 -> A53SS0_0 |集群:2、FIFO:0、用户:0“、这意味着:

- MCU R5F 使用邮箱集群 2、FIFO 0 发送到 A53

- A53 在用户 ID 0(其中断线路)上接收

注意:为了禁用两个内核之间的邮箱通信、应将群集、用户和 FIFO ID 配置为 255。