Other Parts Discussed in Thread: AM62A7-Q1, TPS6594-Q1, TPS6593-Q1, TPS22918, AM62A7, AM6548

器件型号: AM62A74

主题中讨论的其他器件: TPS6594-Q1、 TPS65224、AM62A7-Q1、 TPS6593-Q1、 TPS22918AM62A7、 AM6548

工具/软件:

尊敬的电路板设计人员:

我正在使用 TPS6593 PMIC 设计电路板

我应该了解一些常见的建议或意见吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: AM62A7-Q1, TPS6594-Q1, TPS6593-Q1, TPS22918, AM62A7, AM6548

器件型号: AM62A74

主题中讨论的其他器件: TPS6594-Q1、 TPS65224、AM62A7-Q1、 TPS6593-Q1、 TPS22918AM62A7、 AM6548

工具/软件:

尊敬的电路板设计人员:

我正在使用 TPS6593 PMIC 设计电路板

我应该了解一些常见的建议或意见吗?

尊敬的电路板设计人员:

请参阅以下常见问题解答、常见问题解答和回复

同时、如果您将 SK-AM62A-LP EVM 与 TPS6593 搭配使用 1211. -Q1 PMIC、然后可以修改硬件以更改 VDD_CORE 上的默认电压、该电压由 PMIC 多相 Buck1/2/3 供电。

PMIC 的 GPIO6 配置为以以下极性设置 Buck1/2/3 上的电压:

上电期间、'1211 的 PFSM 在启用 3.3V 负载开关后读取 GPIO6 10ms 的状态。 如果 GPIO6 被上拉至该信号、BUCK123 将为 0.85V。

因此、从 PMIC 的角度而言 、将 GPIO6 拉高至 3.3V 负载开关信号

以下用户指南记录了这些信息以及所有 PMIC NVM 配置: https://www.ti.com/lit/pdf/slvucm3

此致、

Sreenivasa.

尊敬的电路板设计人员:

请参阅以下常见问题解答

完整的 PMIC 可订购器件型号为 TPS65931211RWERQ1 它经过预先编程、以满足 AM62A 处理器的电压和序列要求。 此部件号可在消息中引用的文档的表 2-1 中找到

【常见问题解答】TPS6594-Q1:残余电压检查

此致、

Sreenivasa.

尊敬的电路板设计人员:

将 TPS65224 用于 AM62A

请参阅以下常见问题解答

(38)【常见问题解答】AM62P/AM62P-Q1 设计建议/定制电路板硬件设计–PMIC TPS65224-Q1 的常见问题 — 处理器论坛-处理器 — TI E2E 支持论坛

其他输入

我们收到原理图审阅团队的申请、要求在 PMIC TPS65224 RSTOUT 引脚和 SOC MCU_PORZ 引脚之间添加一个缓冲器。

我认为原因是 SOC MCU_PORZ 需要上升沿和下降沿。 您也想分享详细信息。

(例如 MCU_PORZ 作为输入所需的上升沿压摆率,上升时间等)

PMIC nRSTOUT 是 PMIC 的开漏慢速斜坡输出。

当缓慢斜坡复位输入应用于 MCU_PORz 时、内部复位电路可能会出现干扰。

建议使用分立式推挽输出缓冲器来尽量减少转换。

我们没有 MCU_PORz 的规格。 建议越快越好。 (<10ns)

如果可能、您能否帮助我确认 Buck1 (VDD_CORE) 和 LDO0 (VDDR_CORE) 的时序关系

在启动序列中、Buck1 在 5.9ms 时变为高电平、在 6.45ms 时变为 LDO3 (VDDR_CORE)。 在关断模式下、LDO3 在 0.5ms 时下降、降压 1 在 1ms 时下降。 时序是从使能上升沿/下降沿测量的。

部分 IO - VDD_CANUART(内核电源)是什么?

对于部分 IO、 VDDSHV_CANUART (1.8V/3.3V) 和 VDD_CANUART (0.75V/0.85V) 均连接到常开型电源轨。 当不使用部分 IO 模式时、CANUART 电源 与其余 IO 和内核连接到相同的电源轨。

此致、

Sreenivasa.

电路板设计人员嗨

有关选择 PMIC 的输入:

产品文件夹中建议使用或用于 SK 或 EVM 原理图的 PMIC 在设计时考虑了以下因素:电源时序、电源轨输出转换率、nRSTOUT(复位输出)延迟输出(在所有电源斜升以使时钟保持稳定后)、以及根据处理器最坏情况下的电流消耗确定电源轨的大小。

选择备选非 TI PMIC 时、建议定制电路板设计人员查看相关配套资料(包括数据表和最大额定电流文档)并遵循要求/建议。 建议查看数据表的压摆率要求、上电和断电序列部分、并确认非基于 TI PMIC 的电源架构遵循建议。

需要注意的一点是处理器不支持内核电压或模拟电源的动态调节。

有关电源衰减的常见偏置输入

请参阅以下常见问题解答

我已经将注释放在这两个部分中、因为它适用于上电和断电。 上电序列不应开始、直到所有电源轨都低于 300mV、而在所有电源轨低于 300mV 之前、断电序列不完成。

此致、

Sreenivasa.

尊敬的电路板设计人员:

电源尺寸输入:

使用最大额定电流应用手册与功率估算工具 PET

最大电流应用手册表示一组电压轨的电流消耗。 请注意、预计此电流不一定会在功耗估算工具中复制。 PET 往往会显示更多的平均用例功率、而最大电流应用手册旨在用于确定电源电压大小、因为它允许这些组上具有一定余量的最大瞬态。 不应使用 PET 确定电源尺寸。

功耗估算工具 (PET) 和最大额定电流应用手册有两个不同的用途。 PET 用于估算特定用例/应用的有效功耗。 最大额定电流应用手册可用于在设计定制电源解决方案时确定电源电压

此致、

Sreenivasa.

尊敬的电路板设计人员:

以供参考

(+) TPS6593-Q1:PMIC 编程 — 电源管理论坛-电源管理 — TI E2E 支持论坛

我们销售的所有零件均已预先编程。 在任何情况下、您都不会收到没有编程的部件。

TPS6593-Q1、TPS6593 是器件型号的通用部分。

TPS6593XXXXRWERQ1、XXXX 表示放置在器件上的特定编程、如您在产品页上看到的、所有器件都具有 TPS6593XXXXRWERQ1 命名方案。

您是否无法打开您的器件、如果是、请打开另一个 E2E 工单、以便我们可以在其中解决您的问题、而不是在此处解决您的问题、因为本问题是为了购买不麻烦的 PMIC、谢谢。

此致、

Sreenivasa.

尊敬的电路板设计人员:

仅供参考(可用作参考)

(+) TDA4VM:PMIC 报告 VDD_CPU 过流错误 — 处理器论坛-处理器 — TI E2E 支持论坛

几个要点...

事实上、您看到了这些特定的中断、您应该仔细检查原理图和布局、了解以下两点:

早期版本的 TDA4 SK 和 EVM 在上述两点上出现了一些小错误。 电路板已通电并正常工作、但一些电路板在降压性能方面的稳定性较差。

此致、

Sreenivasa.

尊敬的电路板设计人员:

FYI 板载启动 PMIC 相关

(+) AM62A7-Q1:AM62A7 SoM 未加电 — 处理器论坛-处理器 — TI E2E 支持论坛

FB_B3 不能悬空。 如 PMIC 用户指南中所述: “FB_B3 必须连接到 3.3V。如果在监控器启用时 3.3V 未连接到 FB_B3、则器件进入硬件 SAFE RECOVERY 状态、并且处理器电压被禁用“。

(+) AM62A7:AM62A7 电源时序 — 处理器论坛-处理器 — TI E2E 支持论坛

VDD_CORE 和 VDD 之间的序列要求 R 在上电序列期间必须遵循_core。 这是一项硬性要求。

对于断电、我们强烈建议 在按顺序关闭下一个电源轨 (VDD_CORE) 之前将 VDDR_CORE 放电至~300mV 以下。 但是、我们没有任何数据表明、如果 VDD_CORE 在断电期间放电速度快于 VDDR_CORE、则会出现问题。 该规格中包含这种断电要求、因为在断电期间 VDDR_CORE 上的电势大于 VDD_CORE + 0.18V、这并未经过完全的验证/表征。

此致、

Sreenivasa.

尊敬的电路板设计人员:

附加输入:

如果软件在 SoC 断电之前运行、它下次启动时是否会受到影响?(从硬件角度来看)

在完成软件关闭过程之前触发断电序列是 SoC 的未知状态、其中未定义预期行为。 如果在软件关闭过程中电源发生变化、则可能存在数据损坏的风险。 这是我们建议遵循记录的断电序列并确保在关闭电源之前完成软件关闭请求的原因之一。

此致、

Sreenivasa.

尊敬的电路板设计人员:

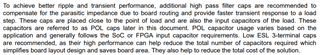

与 3 端电容器相关的输入

对于 TDA4AL PMIC 参考设计原理图、为什么需要使用 4*三端电容? 如果我们不使用、风险是什么?

由于等效串联电感较低、因此与 2 端子等效电容器相比、3 端子电容器在滤除高频时更有效。 如果选择替换这些电容器、频率噪声可能会更多。

TPS6594-Q1 数据表中“应用和实现“一章的“降压输出电容器“小节摘录表明建议使用 3 端电容器。

降压转换器的输入端还有 3 个端子、为什么我们还需要在输入端添加它们? 谢谢!

感谢您的澄清。 我现在看到您的问题中的电容器每个都连接到其中一个降压输入 1-4。 此处使用了 3 端电容器、因为 PVIN 也是一个噪声信号、受益于低电感电容器。 查看 TPS6594-Q1 数据表中的“布局指南“、我们可以发现 PVIN_BN 上去耦电容器最重要的参数是电感。

这些电容器有助于更大限度地降低 2.2MHz 或 4.4MHz 处的降压开关对 VCCA 电源轨的影响。 这些电容器提供电感较低的电容、能够更好地管理高频电流开关。 PVIN_B5 没有其中一个 3 端电容器、因为 BUCK5 的电流消耗相对较低。

此致、

Sreenivasa.

尊敬的电路板设计人员:

与 5V 运行相关的输入

您可以使用 PMIC 效率估算器工具 (PEET) https://www.ti.com/tool/PEET-GUI 来执行此操作 — 在工具中选择 TPS6594-Q1。 两个器件的效率相同。

(+) TPS6593-Q1:具有 5V 输入的 PMIC 运行 — 电源管理论坛-电源管理 — TI E2E 支持论坛

PMIC VPP 电流

t 500mA 就足够了。 注意:VPP 的 1.8V 源应具有内部有源放电功能、该功能在禁用源时将开启、以确保 VPP 在正常运行期间保持为 0V。

TPS65931211-Q1 适用于 AM62A 的 PMIC 用户指南

使用 5V 输入电源

本用户指南中所述的 PDN 是针对 3.3V 输入电源设计的。 但 TPS65931211-Q1

NVM 还支持 5V 输入电源。 TPS65931211-Q1 上的默认 UV 设置会禁用 NVM/OV

VCCA、这样 PMIC 可以使用任一电压 (3.3V 或 5V)。 如果使用 5V 电源、则需要 3.3V 分立式降压稳压器

其中包括 3.3V IO 域、而不是电源开关。 外部 3.3V 降压稳压器可通过 GPIO4 并需要启用

在 10ms 的延迟内从 0V 斜升至 3.3V、此延迟是在 any2active 序列中分配给 GPIO4 的。

LDO1 配置为“旁路“、需要 3.3V 电源。 该 LDO 可由的输出供电

分立式 3.3V 稳压器。 TI 还建议为其余 LDO (LDO3 和 LDO4) 提供分立式电源

3.3V 稳压器、可降低功率耗散。 VIO_IN 也必须由 3.3V 供电。

使用 5V 而不是 3.3V 时、前置稳压器的电压无法直接连接到

VDDSHV_CANUART。 在这种情况下、VDDSHV_CANUART 可由同一个分立式 3.3V 降压稳压器供电

1. PVIN_Bx 是否可以连接到 5V 并且其他电源 (VCCA、VIO_IN、PVIN_LDOx) 都连接到 3.3V、请再次仔细检查?

建议将 PVIN_LDOx 设置为不超过 VCCA 输入电压电源

如果 VCCA 为 3V3、建议不要使用 5V 的 PVIN_Bx。

2.如果可以、在我们的用例中、是否有针对此 PMIC 的特殊使用指南

TPS65931211 的用户指南、我相信您已了解有关将系统输入电压从 3V3 更改为 5V 的讨论。

在第 3.1.2 节中、 点击此处提供指南的链接

有什么建议从你的身边吗? SCH 如下所示。

PS、按如下所示在我们的工程中附加了 PMIC SCH 设计、TI 也将对其进行审查。

我记得这一点、很抱歉、我的理解是、VCCA、PVIN_Bx 和 PVIN_LDOx 的输入电源都将切换到 5V、而不仅仅是少数几个选项。

如果用户可选择在前面提到的 VCCA、PVIN_Bx、以及 PVIN_LDOx 或 3V3 引脚上使用 5V 输入、则使用 3V3 时、他们需要选择一个输入并使用所有这三个输入、请让他们查看用户指南中的第 3.1.2 节

(+) AM62A7:运行期间发生内核紧急情况 — 处理器论坛-处理器 — TI E2E 支持论坛

AM62A7:运行期间发生内核紧急情况

我们已确定根本原因并解决了该问题。

该问题与 VCC_CORE 电压有关。

根据我们电路板的硬件设计、VCC_core 应该为 0.85V、但实际上在 0.75V 下测得。

我们的电路板经过设计、通过上拉 PMIC GPIO6 将 VCC_core 设置为 0.85V。

由于电路板上的 VIO_IN 为 1.8V、因此我们最初将 PMIC GPIO6 上拉至 1.8V。

然而、在测试期间、我们发现当 GPIO6 上拉至 3.3V 时、VCC_core 仅达到 0.85V。

我查看了 PMIC 数据表、但找不到任何提及 GPIO 输入阈值电压的内容。

我最初假设上拉电压应与 VIO_IN (1.8V) 匹配、但在这种情况下、PMIC 似乎需要 3.3V 上拉电阻以便 GPIO6 按预期运行、而与 VIO_IN 无关。

感谢您检查 PMIC GPIO6 的建议、我们能够解决这个问题。

(+) AM62A7:VCC_CORE 电源的 PMIC 控制问题 — 处理器论坛-处理器 — TI E2E 支持论坛

在 SoC 和外设之间共享 3.3V/1.8V 电源时、必须考虑时序、压摆率和安全 IO 要求。 大多数处理器 IO 都没有失效防护功能。 外设/连接器件的 IO 电源必须 与处理器双电压 VDDSHV 电源共享相同的电源。 这可确保仅当相应的 VDDSHV 具有有效电压电平时才为 IO 供电。

有关更多信息、请参阅处理器产品页面的“技术文档“下提供的硬件设计注意事项和设计指南文档。

此致、

Sreenivasa.

尊敬的电路板设计人员:

与 SD 卡电源控制相关的输入

(+) TPS6593-Q1:用于 SD 卡接口的 LDO1 输出 — 电源管理论坛-电源管理 — TI E2E 支持论坛

TPS6593-Q1:用于 SD 卡接口的 LDO1 输出

n 如果客户不使用 UHS-I 速度、而电源开关控制 SD 卡电源、且未实现电源开关 EN 逻辑、是否建议连接 GPIO11。

简而言之、建议将 GPIO11 接地、现在 GPIO11 连接到启用 LDO1。

TPS65931211 上的 GPIO11 设置:

至于 LDO1 的输出设置:

如果我可以总结输入、启用 LDO1 的唯一方法是在 nRSTOUT 引脚变为高电平后、GPIO11 的输入从低电平变为高电平。

正确。

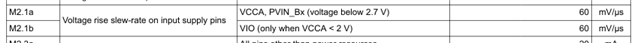

我怀疑在连接任何开关 3.3V 电源时、对于输入压摆率没有问题。

从上面的行项目来看、PIN 存在限制、只是为了提高认识、但很少会违反此规定。 这些行项目意味着 VIO_IN 应该 不会 在 VCCA/PVIN 引脚之前斜升、但 PMIC 侧没有问题。

此致、

Sreenivasa.

尊敬的电路板设计人员:

与电源转换相关的输入

(9) AM6548:确认压摆率 — 处理器论坛-处理器 — TI E2E 支持论坛

µs AM6548 的数据表、对于一般电源、建议最大压摆率小于 100mV/μ s、µs 对于 VDDA_1P8_SERDES0 电源、建议最大压摆率小于 40mV/μ s。 或者、转换时间必须分别大于电源值 x 10µs 和大于电源值 x 25µs。

这只是为了确认、该压摆率同时适用于上升和下降时间?

数据表中定义的最大电源压摆率要求仅在电源轨斜升时适用。 在电源轨上实施的 ESD 电路可能会误触发、从而在电源轨斜升过快时将电源轨钳位到 VSS。

此致、

Sreenivasa.

尊敬的电路板设计人员:

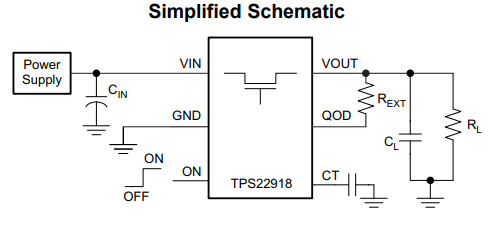

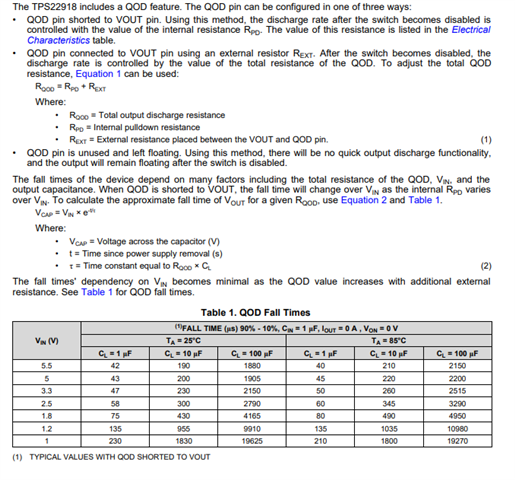

与负载开关压摆率控制、QOD 和输出电容相关的输入。

https://www.ti.com/lit/ds/symlink/tps22918.pdf

9.2.2.1 输入电容器 (CIN)

限制在开关导通至 A 时由瞬态浪涌电流引起的输入电源压降

放电的负载电容器或短路、需要在 VIN 和 GND 之间放置一个电容器。 1 µF 陶瓷电容器

靠近引脚放置的电容器 CIN 通常就足够了。 可以使用更高的 CIN 值进一步减小

电流应用期间的压降。 开关重负载时、建议使用

输入电容器比输出电容器高大约 10 倍、避免出现过大的压降。

9.2.2.2 输出电容器 (CL)(可选)

由于 MOSFET 中集成了体二极管、A CIN 大于 CL

转换器。 A CL

当移除系统电源时、大于 CIN 可能会导致 VOUT 超过 VIN。 这可能会导致电流

从 VOUT 流过体二极管、流向 VIN。 A CIN 到 CL

为了尽可能减小 VIN、建议使用 10 比 1 的比率

启动期间浪涌电流引起的骤降。

8.3.2 快速输出放电 (QOD)

https://www.ti.com/lit/ds/symlink/tps22965.pdf

此致、

Sreenivasa.

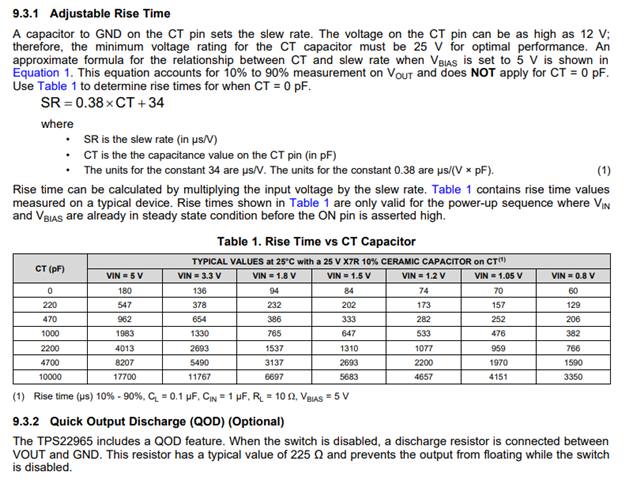

尊敬的电路板设计人员:

与负载开关 实现相关的输入

https://www.ti.com/lit/ds/symlink/tps22965.pdf

10.1.2 输入电容器(可选)

限制在开关导通进入 A 时由瞬态浪涌电流引起的输入电源压降

放电的负载电容器或短路、需要在 VIN 和 GND 之间放置一个电容器。 1-µF 陶瓷电容器

靠近引脚放置的电容器 CIN 通常就足够了。 可以使用更高的 CIN 值进一步减小

电流应用中的压降。 开关重负载时、建议使用

输入电容器比输出电容器高大约 10 倍、避免出现过大的压降。

10.1.3 输出电容器(可选)

由于 NMOS 开关中集成了体二极管、因此强烈建议 CIN 大于 CL。 A CL

当移除系统电源时、大于 CIN 可能会导致 VOUT 超过 VIN。 这可能会导致电流

从 VOUT 流过体二极管、流向 VIN。 建议 CIN 与 CL 的比率为 10:1、以尽可能减少 VIN 骤降

由启动期间的浪涌电流引起;但是、为了确保正常、不需要 10:1 的电容比

输入和输出功能。 小于 10:1 的比率(例如 1:1)可能会导致 VIN 骤降略微增加

因浪涌电流而导通。 可以通过延长 CT 引脚上的电容来减少这种骤降

上升时间(请参阅可调节上升时间部分)。

此致、

Sreenivasa.

尊敬的电路板设计人员:

与 PMIC 用例相关的输入

我 对处理器的 PDN 设计有疑问。 是否可以不使用 PMIC? 我可以改用大量简单的直流/直流转换器吗? 我想简化我的设计。

这是可能的、但不建议这样做。 处理器已使用 PMIC 进行了测试、因此已 通过处理器验证了其负载阶跃响应、噪声水平、电源轨序列控制等。 我不确定如何简化一堆分立式电源和序列发生器。

您需要确保分立式电源架构遵循处理器特定数据表中规定的电源序列、提供在电源斜升后将处理器热复位输入置为有效之前所需的延迟、根据最大电流确定电源电 压尺寸应用手册、遵循压摆率要求、支持残余电压检测、并允许在电源斜降至<300mv 后为 PMIC 供电

此致、

Sreenivasa.

尊敬的电路板设计人员:

仅供参考、与看门狗相关的输入

触发看门狗时、是否存在允许控制器记录一些故障状态的短暂延迟? 或 TPS6594-Q1 它会立即关断所有电源轨?

您是否在寻找一种方法让处理器知道导致看门狗超时的原因、或者您能否详细说明用例、以便我们能够根据客户所需的解决方案来找到问题的最佳答案? 此外、客户是否已经考虑了 TPS6594 的特定 OPN(如果是,我们可以检查更具体的 NVM 设置)、或者他们是否希望 实现自己的自定义 NVM?

根据数据表第 8.3.11.1 节:看门狗故障计数器和状态: www.ti.com/lit/gpn/tps6594-q1

您可以由此了解我询问他们使用的 NVM 配置的原因、因为有很多选项、这取决于您如何设置器件。 但我想强调的是、根据具体用例、您可以设置 WD 中断阈值、以便处理器在发生足够的 WD 故障事件以达到 WD_RST_TH 之前在 nINT 引脚上收到警告。 此外、通过的 WD_RST_TH 也可以向状态机生成 WD_ERROR 触发条件、PFSM 可以定义 PMIC 的反应方式。

您能分享一下他们选择的 OPN 或者他们是否正在进行新的开发吗?

此致、

Sreenivasa.