“线程: 测试”中讨论的其它部件

大家好,团队

我的客户在 定制板上使用66AK2H14时遇到了一个非常具体的问题。

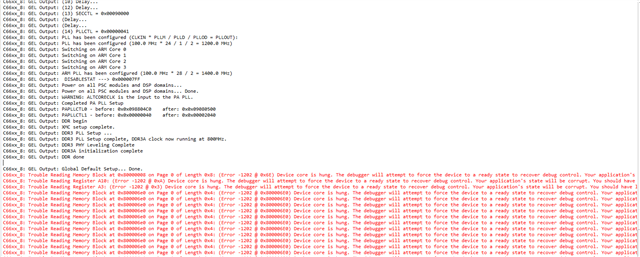

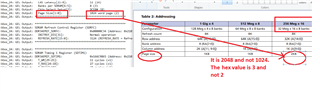

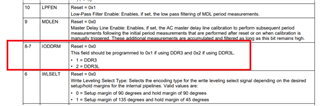

连接到目标后,他运行 gel 文件以初始化 SoC (默认情况下与该版本 CCSv910上的 gel 非常相似,即在下面登录)。 但是,即使 DDR3似乎初始化正确,DDR3访问(例如通过内存浏览器或 通过 ddr3A_MEMOR_TEST ()函 数直接访问)也会导致 CPU 崩溃。

仿真器是 XDS560V2STM 和 CCSv910

-CCS 发送错误 -1202 (如下面)。 https://software-dl.ti.com/ccs/esd/documents/ccs_debugging_jtag_connectivity_issues.html#device-hung 未指定此错误

-JTAG 测试证明与 DDR 的物理互连是正确的。

CPU 和 DDR 的电源电压都经过测试,没有发现任何问题。

-> DDR 访问如何使 CPU 崩溃?

->您是否对要执行的测试有任何解释或建议?

->我在 https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1014972/66ak2g12-what-s-this-error-message-of-ccs-ddr-access-by-memory-browser/3751531?tisearch=e2e-sitesearch&keymatch=ERROR%201202#3751531网站上看到了一篇非常相似的帖子 ,但没有得到正确的回答,自那以后您是否找到了一个解决方案?

此致,

Geoffrey

连接到目标时出错:(错误-1202 @ 0x6E)设备核心挂起。 调试器将尝试强制设备进入就绪状态并恢复调试控制,但应用程序的状态将被破坏。 您对内存和寄存器的访问权限应该有限,但您可能需要重置设备以进一步调试。