大家好,

J721E 上的8个端口按这种方式划分

RGMII 端口- 1,3,4,8。 QSGMII 端口- 2,5,6,7

1. CPSW Mac 端口按顺序映射到 PHY。 MAC0->RGMII 端口1,MAC1->RGMII 端口3等。 我是对的吗?

2.如果上述情况属实,是否可以将 CPSW Mac 端口重新配置为任何 RGMII/SGMII phy?例如,我可以将 MAC8映射/配置为 QSGMII 端口6?

谢谢,

维沙尔·库尔卡尼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,

J721E 上的8个端口按这种方式划分

RGMII 端口- 1,3,4,8。 QSGMII 端口- 2,5,6,7

1. CPSW Mac 端口按顺序映射到 PHY。 MAC0->RGMII 端口1,MAC1->RGMII 端口3等。 我是对的吗?

2.如果上述情况属实,是否可以将 CPSW Mac 端口重新配置为任何 RGMII/SGMII phy?例如,我可以将 MAC8映射/配置为 QSGMII 端口6?

谢谢,

维沙尔·库尔卡尼

Vishal,

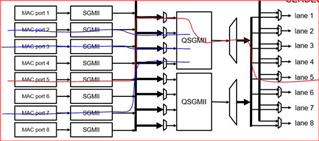

8个 CPSW MAC 都可以配置为 RGMII,SGMII 或 QSGMII 端口。 对于 RGMII 和 SGMII,端口号标记为端口1,2,... 8。 因此,RGMII 仅受引脚粘性限制,而 SGMII 仅受 SERDES 粘性方案限制。

关于索引的警告词-请注意,端口0通常指主机端口。 但是,在 TRM 中,对于为端口建立索引的寄存器地址,j=0表示端口1。

对于 QSGMII,四个 GbE 共享一条通用的5Gbps SERDES 通道。 有两个基于 SERDES mu兴 的 QSGMII 接口,因此您可以按以下方式分配端口:

例如,在 EVM 上,我们将 QSGMII 连接到四以太网子卡,并且根据 连接到 CPSW 端口2的 SERDES mux,将 SERDES0 Lane 1配置为 QSGMII。 因此,我们将 CPSW 端口2设置为主要 QSGMII 端口,映射到外部 QSGMII PHY 上的端口0。 其他三个端口(端口1,3,4)设置为 QSGMII 子模式,如下所示:

|

QSGMII PHY 端口0 |

CPSW 端口2 |

|

QSGMII PHY 端口1 |

CPSW 端口1 |

|

QSGMII PHY 端口2 |

CPSW 端口3 |

|

QSGMII PHY 端口3 |

CPSW 端口4 |

详细的集成视图如下所示,此信息不在 TRM 中。

此致

华普