您好,支持团队,

我收到了客户的以下问题。

*客户问题*

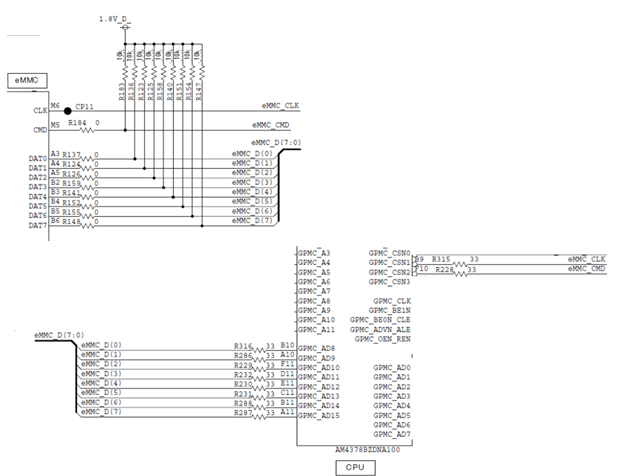

将eMMC连接到CPU的MMC1时,可能会出现这种情况

内部下拉(10.58k至34.61kΩ μ s)产生中间电位,

eMMC的外部上拉电阻(10kΩ Ω)和内部上拉电阻(10k至150kΩ Ω)

在CPU重置期间(以及释放重置后的立即)。 这是个问题吗?

以下是对上述条件的说明。

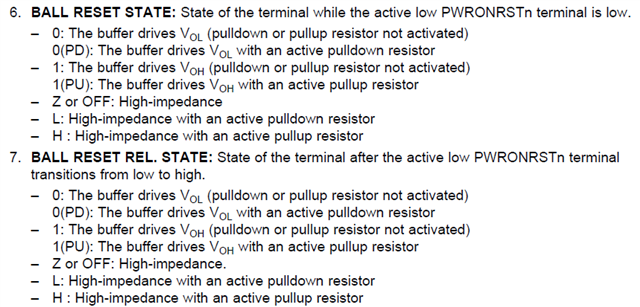

CPU内的下拉电阻器

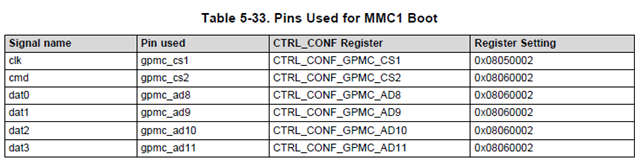

AM437X技术参考手册“5.2 .6.5 8 Pins Used (使用了8针脚)”说明了这一点

引导MMC1时,应将dat0-3分配给GPMC_ad8,GPMC_ad9,GPMC_ad10和GPMC_ad11。

检查表4-10,数据表中的针脚属性,gpmc_ad8,gpmc_ad9,gpmc_ad10,

和GPMC_ad11具有球重置状态和球重置REL。 状态设置为"L"并被下拉

内部。

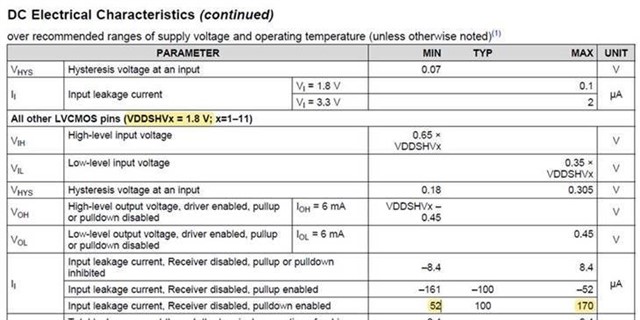

CPU内的下拉电阻值计算如下。

具有内部电阻的所有其它LVCMOS引脚(VDDSHVx = 1.8 )均可用于下拉

VDDSHVx = 1.8

最小内部电阻 = 1.8V/170μA = 10.58kΩ Ω

最大内部电阻 = 1.8V/52μA = 34.61kΩ Ω

外部上拉电阻器

查看示意图核对表,有一节" 2.6 MMC/"说明

-连接设备(卡或eMMC)时,请在RST#,CMD和所有DAT信号上包括10k上拉电阻。

建议在n ü 10kΩ 上使用外部上拉。

此外,JEDEC标准(JESD84-B50)“10.3 4总线信号线路负载”

还列出了一个10至100kΩ Ω 的外部上拉电阻,作为eMMC的DAT1-7的要求。

eMMC的内部上拉电阻

JEDEC标准(JESD84-B50),“10.3 4总线信号线路负载”状态

内部上拉电阻DAT1-DAT7被描述为10k至150kΩ Ω。

如果您有不清楚的地方,请告诉我。

此致,

Kanae