主题中讨论的其他部件:TLV320AIC3104,

您好,支持团队,

我的客户有关于AM437x处理器的McASP的以下问题。

我们正在原型板上检查运行情况,我们认为存在问题

与McASP的工作方式以及创建主板时假定的连接。

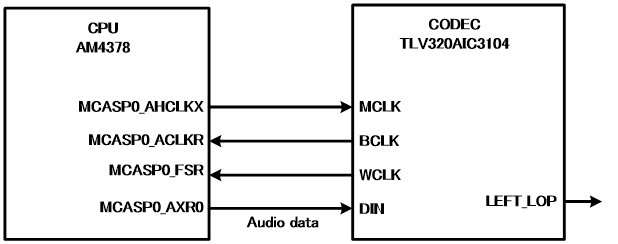

CPU (AM4378)与编解码器(TLV320AIC3104)之间的连接关系

原计划如下。

-从CPU向COEDC提供MCLK

编码解码器在主模式下运行

-将BCLK和WCLK编解码器分配给CPU

-将音频数据从CPU输出到编解码器

-DA音频编解码器通过AWAMP通过扬声器播放

参考图:最初计划的连接

在设计时,我的理解不够充分,但我已重新检查

AM437x技术参考手册“24.3 5时钟和帧同步发生器”

和应用程序报告SPRACK0,并具有以下确认/问题。

请回答以下问题。

问题1. 以下各项认可是否正确?

要将数据从CPU输出到编解码器,需要路由到内部数据传输XCLK和内部帧同步。

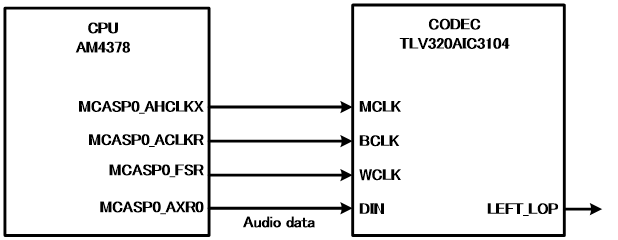

从外部到McASP0_ACLKR和McASP0_FSR引脚的CLK输入可以路由到RCLK和内部帧同步进行接收。

XCLK和内部帧同步无法路由到XCLK和内部帧同步进行传输,因此无法按预期方式使用。

-例如,如果编解码器的BCLK和WCLK连接到McASP0_ACLKX和McASP0_FSX引脚,

它们可用于最初设想的配置。

由于McASP0_ACLKX和McASP0_FSX不仅能够路由以发送,而且还能接收RCLK

内部帧同步,BCLK和WCLK可以路由到McASP0_ACLKX和McASP0_FSX,而无需考虑数据传输

或接收,主模式或从属模式配置。 只要连接了ACLKX和McASP0_FSX,就可以使用它们。

问题2. 如果我们想在不修改主板的情况下支持此功能,是否可以使用以下配置?

信号输入/输出关系应如下所示:CPU为主,编解码器从模式,

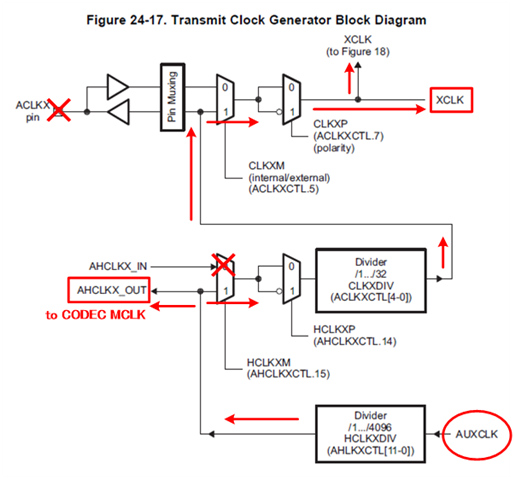

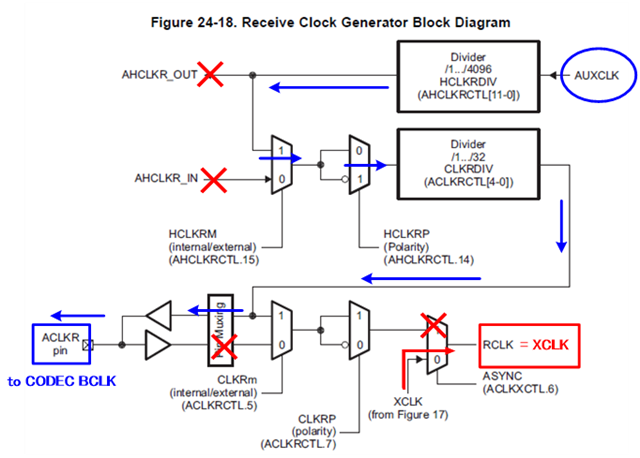

CPU内部McASP时钟的路由应如下所示。

在发送和接收的方框图中,假设分频器的分频器比率已对齐。

下图中,AUXCLK在发送时显示为红色,在接收时显示为蓝色,

但是,如果源相同,则假定它是同步的。

传输时钟发生器方框图

接收时钟发生器方框图

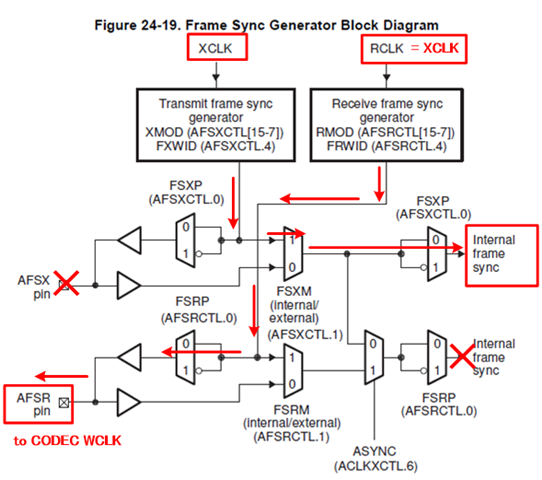

帧同步生成器方框图

请解释此配置,它通常不使用。

不过,我们需要考虑可否在不改动主板的情况下处理这项问题。

如能立即支持上述问题,将不胜感激。

我希望得到您的及时回复,或者至少提供此回复的时间表。

此致,

Kanae