您好,支持团队,

我对输入信号上升时间和输入信号下降时间的最小值有疑问。

问题1:关于数据表"MMC. 17.1 5.12 电气数据和定时"中的输入信号上升时间和输入信号下降时间,

是否需要严格遵守最小值1ns?

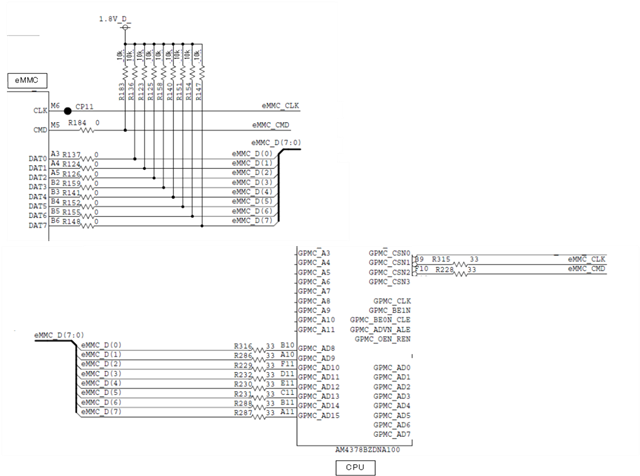

当前示意图如下所示。

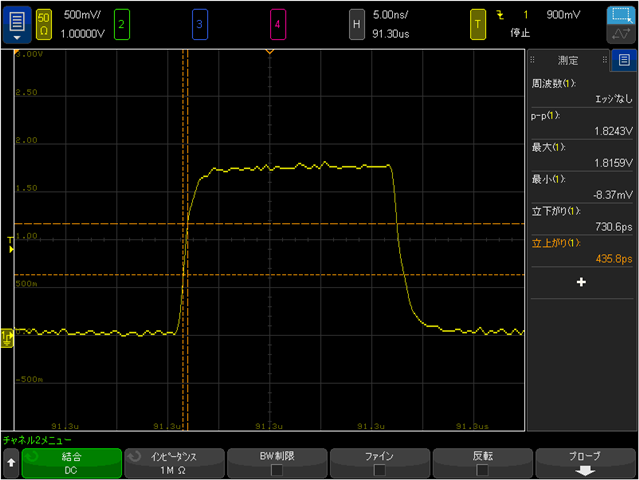

DAT3从eMMC到CPU的波形如下所示。

时间轴刻度没有相对于过渡时间进行扩展,但它在400到500 ps之间。

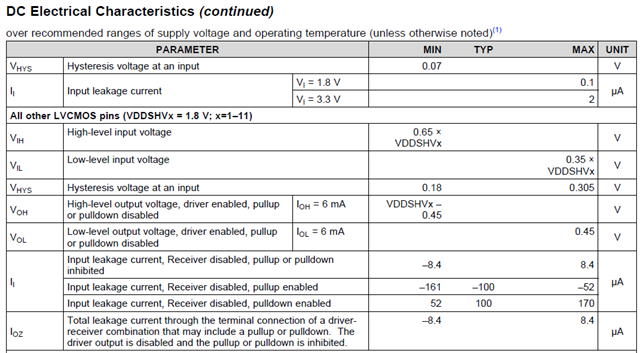

上升时间阈值如下所示

VILmax:0.65 * 1.8 = 0.63V

VIHMIN:0.35 * 1.8 = 1.17V

*与1.8V VCCQ一起使用

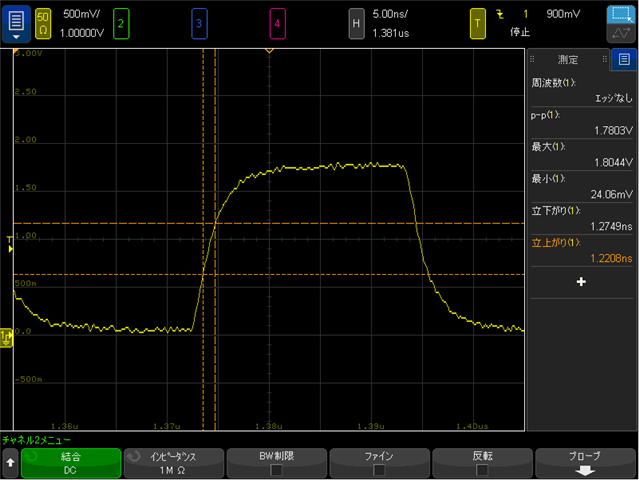

恒定变化后的波形如下所示。

更改后的常量如下所示

CPU侧的阻尼电阻器:56Ω Ω

eMMC侧的阻尼100Ω:μ A

CMD和数据(7:0)线路上的外部上拉电阻器(eMMC附近的上拉电阻):10 kΩ

问题2. 我检查了以下线程。是否将上升时间从10 % 指定为90 % ,而不是从VILmax指定为VIHMIN?

e2e.ti.com/.../am437x-input-signal-rise-time-and-fall-time-from-nand-flash-memory

对于eMMC,JEDEC将VILmax指定为VIHMIN,因此我们测量了相同的时间段。

此致,

Kanae