大家好、

以下是客户可能需要您帮助的几个问题:

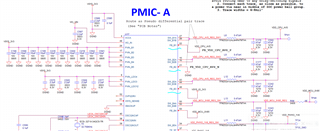

在上述参考设计中、三个 SWB1A、SWB2A、SWB3A 输出组合成一个输出 VDD_CPU_AVS:

1) 1)在 P44上、需要 FB_B1和 FB_B2使用类差分路由、原因是什么?

2) 2)在 P44上、FB_B2直接连接到 DGND、原因是什么?

3) 3)在 P44上、U17芯片 FB_B3连接到 VSYS_IO_3V3、这是 U27的输出电压。

是否用于 VSYS_IO_3V3的电压监控? 详细的监控是如何工作的、以及如何启用此监控功能? 是否有任何文档可供参考?

4) 4)在 P45上、VSYS_IO_3V3连接到 U8芯片的 FB_B4、还用于电压监控 VSYS_IO_3V3。

重复 VSYS_IO_3V3的电压监控是否冗余? 或者是否有任何特殊考虑?

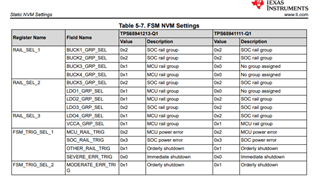

5) 5) 输入电压和输出电压由 PMIC 芯片 TPS65941监控。 PMIC 会发生什么情况、或者当 Vout/Vin 超过阈值时、接下来会采取什么措施?

您可以帮助检查此案例吗? 谢谢。

此致、

樱桃