Thread 中讨论的其他器件:SysConfig、

大家好、AM4团队、

未解决/未完成的参考 E2E: https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1102863/am4378-pru-and-spi0-nor-flash-pin-mapping-uboot-partitions

我的客户有以下问题。

我们的团队需要对 SPI0 NOR 闪存的使用进行澄清。 感谢您对此做出的回应。

目前、我们使用 SPI0 NOR 闪存来引导电路板。 除了其他现有 UART 外、我们还需要将 PRU ICSSS 0 UART 用于串行通信。 但这会与我们正在寻找将 SPI0 NOR 闪存交换到其他一些引脚的引脚发生冲突。 这里、我们不使用存储了 MLO 的 NOR 闪存默认 SPI0引脚来引导器件、而是使用备用 SPI0引脚(SPI0_CS0;AD25、SPI0_D1;AB25、SPI0_SCLK; AE21)用于连接 SPI NOR 闪存。 如果我们将 SPI NOR 闪存移至备用 SPI0引脚、我们需要了解引导 ROM 是否能够检测 SPI NOR 闪存。

由于 SPI0默认引脚与 PRU ICSS 0冲突、我们还将评估将 SPI NOR 闪存放到 eMMC 引导0/boot1分区中并加载 MLO 的替代方法。 这不是 eMMC (FAT32)的第一个 FAT 分区。 这是 eMMC 供应商提供的用于存储引导加载程序/引导配置数据的引导区域。 我们需要了解当前的 TI uBoot 是否支持引导0/boot1分区以及安全引导实现。

此外、我们观察到从 SPI0 NOR 闪存加载 MLO 大约需要10到15秒。 是否有办法对此进行优化?

我们的团队需要对 SPI0 NOR 闪存的使用进行澄清。 感谢您对此做出的回应。

谢谢、Merril

「香港

Brad Caldwell 回复了。

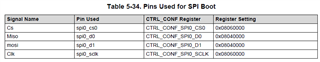

对于 SPI 引导、ROM 代码将引脚多路复用寄存器配置为使用以下 TRM 表5-34中定义的引脚。 遗憾的是、这是硬编码的、没有任何选项可以更改它。

我在 https://dev.ti.com/sysconfig 上使用 SysConfig 工具进行了快速浏览 、您说得对、与 PRUICSS0 UART 引脚存在直接冲突。 我看不到任何引脚复用选项可以解决这个问题。 我确实看到 PRUICSS1 UART 没有冲突、但这当然取决于您是否已经将这些引脚用于其他用途。

我想我之前没有看过它、但也许有一种从 SPI0引导的方法、然后在引导之后重新配置 PRUICSS0 UART 的引脚、然后在此时使用 UART。 这可能需要更改电路板以某种方式添加由 GPIO 控制的外部多路复用器、以确保 UART 和 SPI 或闪存在一种或另一种模式下不会发生冲突。

我必须让我们的 Linux 专家回答有关 eMMC 引导的问题、但我要说、eMMC 是引导和存储文件系统的常用方法。 我首先在 SDK 中查看 U-Boot 文档。 以下部分介绍了 eMMC 分区

「香港

尊敬的 TI Linux 专家:

有更新吗? 此外、客户 还询问... "我们期待着对有关从 TI 引导 ROM 中的 eMMC Boot0/boot1加载 MLO 的查询作出响应。 此外、我们还需要有关 AM4378 TI U-Boot 版本提供的 eMMC Boot0/boot1分区支持的信息。 我们最近的测试表明、从 SPI NOR 闪存加载 MLO 需要从 HS 板上的 TI 引导 ROM 大约15秒的时间。 但是、使用 SD 卡时、引导仍然正常。 因此、我们需要将 eMMC 评估为引导器件、而不是 SPI NOR、因此澄清我们先前在此主题中的问题至关重要。 请尽快告知我们您的回复。"

谢谢、Merril