我对 A15和 DSP 之间的连接有疑问。 我们正努力验证概念:通过 PCIe 将 FPGA 连接到 DSP。

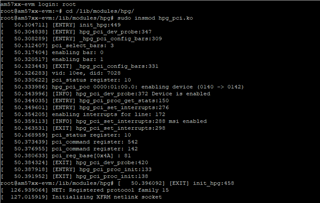

作为具有 Linux 经验的人、我决定首先使用 A15作为桥梁。 此桥只是一个简单的 PCIe 驱动程序、它使用 Linux 内核 API、在接收到一些数据后、它将触发 DSP 来处理接收到的数据。 它在另一侧的工作方式相同:DSP->A15->PCIe->FPGA。

第一个问题:

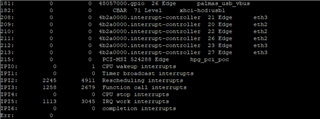

我不知道如何在 DSP 和 A15之间建立连接。 我想到了在 DTS 中定义的共享存储器、并通过资源表传播到 DSP。 在这种情况下、DSP 将由 A15侧的简单 IRQ 触发。 您对此想法有何看法? 它是否良好? 我们需要非常低的事务延迟。

我一直在与 J6+和 J6Eco SoC 合作,就我所记得的您(德州仪器)提供的 VSDK 而言,它具有非常大的延迟。 但是、您是否有一些类似的框架、但性能更好?

第二个问题:

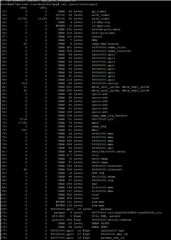

我们应该如何加载 DSP? 我知道有一种机制叫做“提早启动”,但直到一切都不稳定为止,我对这种机制不太担心。 我们是否可以在 uboot 和 DTS 中禁用 Early boot、然后通过 Remoteproc 机制加载 DSP 映像?

此致 Bernd