大家好、

客户正在将 AM3505AZER 与 PHY 搭配使用、并希望知道包含该变化的内部上拉/下拉寄存器值

请提供。

数据表中有 II:双电压 IO 引脚的输入电流规格,如下所示。 寄存器似乎是电流源。 在本例中、我们可以通过计算获得它吗? 如何计算?

以下计算是否正确? 我不能 μA 数据表中关于具有100 μ A 上拉电阻的输入引脚启用的说明。

- 上拉

- VDDSHV = 3.3V,上拉:3.3/310=10.6K 欧姆(最小值) 3.3/70=47.1K 欧姆(最大值)

- VDDSHV = 1.8V,上拉:1.8/310=5.8K 欧姆(最小值) 1.8/70=25.7K 欧姆(最大值)

- 下拉

- VDDSHV = 3.3V,下拉:3.3/270=12.2K 欧姆(最小值) 3.3/75=44.0K 欧姆(最大值)

- VDDSHV = 1.8V,下拉电阻:1.8/270=6.7K 欧姆(最小值) 1.8/75=24.0K 欧姆(最大值)

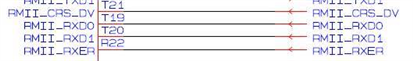

・RMII_CRS_DV(T21)

・RMII_RXD0(T19)

・RMII_RXD1(T20)

・RMII_RXER(R22)

谢谢、此致、

Kuerbis