Other Parts Discussed in Thread: 66AK2H06

您好!

我们正在使用66AK2H06开发定制板。 尽管我们查看了 EVMK2H 以供参考、但我们的设计不会将评估板一一一复制到一。

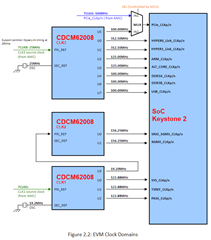

考虑时钟域、如 http://wfcache.advantech.com/www/support/TI-EVM/download/XTCIEVMK2X_Technical_Reference_Manual_Rev1_0.pdf图2.2所示:

此图将 ARM_CLKp/n 指定为125MHz、将 SYS_CLKp/n 指定为122.88MHz。

我们将 Advantech 网站 http://wfcache.advantech.com/www/support/TI-EVM/Rev4_0/BMC/BMC_EVMK2K_1_0_2_6-20160330.zip 上的主板管理控制器(BMC)用作参考。 我要澄清的一点是、引导模式引脚值。 在 ks2evm-bmc-v1.0.2.6\bmc\src\bmc_state.c 中有一个定义:

static BOOTMODE BOOT_MODES[16] =

{ // DIP

{0x00000000, 0x00110CE7, "ARM NAND"}, // 0000

{0x00000000, 0x00100001, "DSP No-Boot"}, // 0001

{0x00000000, 0x00112005, "ARM SPI"}, // 0010

{0x00000000, 0x00100003, "ARM I2C"}, // 0011

{0x00000000, 0x00100CEF, "ARM UART"}, // 0100

...

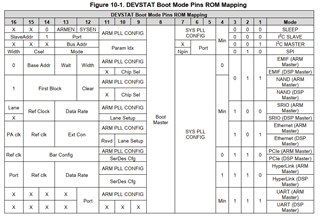

考虑"ARM_NAND"模式、该模式定义为0x00110CE7。 这些值定义了 BOOTMODE[15:0]引脚和 LENDIAN 输入。 就我从代码中追溯到的而言、配置字的 LSB 对于所有配置都是1、是 LENDIAN 值、一个使系统具有小端字节序。 然后、高位将与图10-1中的表中的引导模式值匹配。 K2H 数据表中的 DEVSTAT 引导模式引脚 ROM 映射。

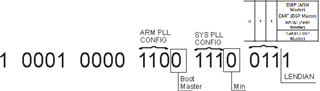

因此、我为0x00110CE7进行以下映射:

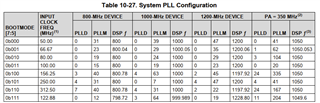

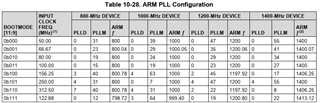

在这里、我将 SYS PLL 配置解码为0b111、将 ARM PLL 配置解码为0b110。 然后、根据表10-27。 系统 PLL 配置和表10-28。 ARM PLL 配置

我对 SYS PLL 配置非常满意、因为0b111可使 DSP 的最高时钟速度 超出122.88MHz 时钟、正如 Advantech 手册中所述。 但是、如果我们看一下 ARM PLL 配置、它的值0b110表明 ARM 内核的最高速度将由312.50MHz 时钟产生。 但是、Advantech 手册中的时钟图(具有蓝色 CDCMS 的时钟图)显示 ARM_CLKp/n 为125MHz。 该值将产生不到顶臂时钟速度的一半。

我可能遗漏了一些非常重要的东西、因此请专家澄清并指导我完成这一过程。

提前感谢。