Thread 中讨论的其他器件:SysConfig、

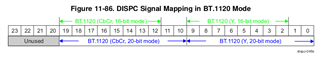

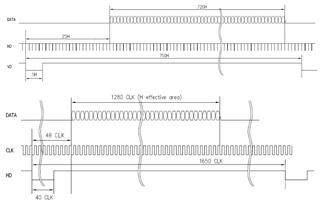

我想将带有 bt1120的视频输出到 AHD 编码器, 我使用 PDK 进行测试,修改示例:vps_examples_dss_BareMetal, 它将显示色条但失败,无信号输出,DISPC 寄存器值为:

DISPC_DISPC_REVISION 0x00000051 DISPC_DISPC_SYSCONFIG 0x00000001 DISPC_DISPC_SYSSTATUS 0x00000001 DISPC_DISPC_IRQSTATUS 0x00000022 DISPC_DISPC_IRQENABLE 0x00004622 DISPC_DISPC_CONTROL1 0x00000309 DISPC_DISPC_CONFIG1 0x01200C04 DISPC_DISPC_DEFAULT_COLOR0 0x00101010 DISPC_DISPC_DEFAULT_COLOR1 0x00000000 DISPC_DISPC_TRANS_COLOR0 0x00000000 DISPC_DISPC_TRANS_COLOR1 0x00000000 DISPC_DISPC_LINE_STATUS 0x00000171 DISPC_DISPC_LINE_NUMBER 0x0000031B DISPC_DISPC_TIMING_H1 0x14100727 DISPC_DISPC_TIMING_V1 0x00501404 DISPC_DISPC_POL_FREQ1 0x0000F000 DISPC_DISPC_DIVISOR1 0x00010001 DISPC_DISPC_GLOBAL_ALPHA 0xFFFFFFFF DISPC_DISPC_SIZE_TV 0x00000000 DISPC_DISPC_SIZE_LCD1 0x031F04FF DISPC_DISPC_GFX_BA_j_0 0x00000000 DISPC_DISPC_GFX_BA_j_1 0x00000000 DISPC_DISPC_GFX_POSITION 0x00000000 DISPC_DISPC_GFX_SIZE 0x00000000 DISPC_DISPC_GFX_ATTRIBUTES 0x000000A0 DISPC_DISPC_GFX_BUF_THRESHOLD 0x04FF04F8 DISPC_DISPC_GFX_BUF_SIZE_STATUS 0x00000500 DISPC_DISPC_GFX_ROW_INC 0x00000001 DISPC_DISPC_GFX_PIXEL_INC 0x00000001 DISPC_DISPC_GFX_TABLE_BA 0x00000000 DISPC_DISPC_VID1_BA_j_0 0x80000400 DISPC_DISPC_VID1_BA_j_1 0x00000000 DISPC_DISPC_VID1_POSITION 0x00000000 DISPC_DISPC_VID1_SIZE 0x02CF04FF DISPC_DISPC_VID1_ATTRIBUTES 0x02288A35 DISPC_DISPC_VID1_BUF_THRESHOLD 0x07FF07F8 DISPC_DISPC_VID1_BUF_SIZE_STATUS 0x00000800 DISPC_DISPC_VID1_ROW_INC 0x00000001 DISPC_DISPC_VID1_PIXEL_INC 0x00000001 DISPC_DISPC_VID1_FIR 0x04000400 DISPC_DISPC_VID1_PICTURE_SIZE 0x02CF04FF DISPC_DISPC_VID1_ACCU_j_0 0x00000000 DISPC_DISPC_VID1_ACCU_j_1 0x00000000 DISPC_DISPC_VID1_FIR_COEF_H_i_0 0x00800000 DISPC_DISPC_VID1_FIR_COEF_H_i_1 0x0E7DF601 DISPC_DISPC_VID1_FIR_COEF_H_i_2 0x2172F102 DISPC_DISPC_VID1_FIR_COEF_H_i_3 0x3762F001 DISPC_DISPC_VID1_FIR_COEF_H_i_4 0xF24E4EF2 DISPC_DISPC_VID1_FIR_COEF_H_i_5 0xF06237F6 DISPC_DISPC_VID1_FIR_COEF_H_i_6 0xF17221FA DISPC_DISPC_VID1_FIR_COEF_H_i_7 0xF67D0EFE DISPC_DISPC_VID1_FIR_COEF_HV_i_0 0x00800000 DISPC_DISPC_VID1_FIR_COEF_HV_i_1 0x0E7DF6FE DISPC_DISPC_VID1_FIR_COEF_HV_i_2 0x2172F1FA DISPC_DISPC_VID1_FIR_COEF_HV_i_3 0x3762F0F6 DISPC_DISPC_VID1_FIR_COEF_HV_i_4 0xF24E4E00 DISPC_DISPC_VID1_FIR_COEF_HV_i_5 0xF0623701 DISPC_DISPC_VID1_FIR_COEF_HV_i_6 0xF1722102 DISPC_DISPC_VID1_FIR_COEF_HV_i_7 0xF67D0E01 DISPC_DISPC_VID1_CONV_COEF0 0x01670100 DISPC_DISPC_VID1_CONV_COEF1 0x01000000 DISPC_DISPC_VID1_CONV_COEF2 0x07A90749 DISPC_DISPC_VID1_CONV_COEF3 0x00000100 DISPC_DISPC_VID1_CONV_COEF4 0x000001C6 DISPC_DISPC_VID2_BA_j_0 0x00000000 DISPC_DISPC_VID2_BA_j_1 0x00000000 DISPC_DISPC_VID2_POSITION 0x00000000 DISPC_DISPC_VID2_SIZE 0x00000000 DISPC_DISPC_VID2_ATTRIBUTES 0x00008400 DISPC_DISPC_VID2_BUF_THRESHOLD 0x07FF07F8 DISPC_DISPC_VID2_BUF_SIZE_STATUS 0x00000800 DISPC_DISPC_VID2_ROW_INC 0x00000001 DISPC_DISPC_VID2_PIXEL_INC 0x00000001 DISPC_DISPC_VID2_FIR 0x04000400 DISPC_DISPC_VID2_PICTURE_SIZE 0x00000000 DISPC_DISPC_VID2_ACCU_j_0 0x00000000 DISPC_DISPC_VID2_ACCU_j_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H_i_7 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV_i_7 0x00000000 DISPC_DISPC_VID2_CONV_COEF0 0x00000000 DISPC_DISPC_VID2_CONV_COEF1 0x00000000 DISPC_DISPC_VID2_CONV_COEF2 0x00000000 DISPC_DISPC_VID2_CONV_COEF3 0x00000000 DISPC_DISPC_VID2_CONV_COEF4 0x00000000 DISPC_DISPC_DATA1_CYCLE1 0x00000000 DISPC_DISPC_DATA1_CYCLE2 0x00000000 DISPC_DISPC_DATA1_CYCLE3 0x00000000 DISPC_DISPC_VID1_FIR_COEF_V_i_0 0x00000000 DISPC_DISPC_VID1_FIR_COEF_V_i_1 0x0000FE01 DISPC_DISPC_VID1_FIR_COEF_V_i_2 0x0000FA02 DISPC_DISPC_VID1_FIR_COEF_V_i_3 0x0000F601 DISPC_DISPC_VID1_FIR_COEF_V_i_4 0x000000F2 DISPC_DISPC_VID1_FIR_COEF_V_i_5 0x000001F6 DISPC_DISPC_VID1_FIR_COEF_V_i_6 0x000002FA DISPC_DISPC_VID1_FIR_COEF_V_i_7 0x000001FE DISPC_DISPC_VID2_FIR_COEF_V_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V_i_7 0x00000000 DISPC_DISPC_CPR1_COEF_R 0x1344B01D DISPC_DISPC_CPR1_COEF_G 0xF51D4883 DISPC_DISPC_CPR1_COEF_B 0x20DC93EB DISPC_DISPC_GFX_PRELOAD 0x00000100 DISPC_DISPC_VID1_PRELOAD 0x00000100 DISPC_DISPC_VID2_PRELOAD 0x00000100 DISPC_DISPC_CONTROL2 0x00000300 DISPC_DISPC_GFX_POSITION2 0x00000000 DISPC_DISPC_VID1_POSITION2 0x00000000 DISPC_DISPC_VID2_POSITION2 0x00000000 DISPC_DISPC_VID3_POSITION2 0x00000000 DISPC_DISPC_VID3_ACCU_j_0 0x00000000 DISPC_DISPC_VID3_ACCU_j_1 0x00000000 DISPC_DISPC_VID3_BA_j_0 0x00000000 DISPC_DISPC_VID3_BA_j_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H_i_7 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV_i_7 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V_i_7 0x00000000 DISPC_DISPC_VID3_ATTRIBUTES 0x00008400 DISPC_DISPC_VID3_CONV_COEF0 0x00000000 DISPC_DISPC_VID3_CONV_COEF1 0x00000000 DISPC_DISPC_VID3_CONV_COEF2 0x00000000 DISPC_DISPC_VID3_CONV_COEF3 0x00000000 DISPC_DISPC_VID3_CONV_COEF4 0x00000000 DISPC_DISPC_VID3_BUF_SIZE_STATUS 0x00000800 DISPC_DISPC_VID3_BUF_THRESHOLD 0x07FF07F8 DISPC_DISPC_VID3_FIR 0x04000400 DISPC_DISPC_VID3_PICTURE_SIZE 0x00000000 DISPC_DISPC_VID3_PIXEL_INC 0x00000001 DISPC_DISPC_VID3_POSITION 0x00000000 DISPC_DISPC_VID3_PRELOAD 0x00000100 DISPC_DISPC_VID3_ROW_INC 0x00000001 DISPC_DISPC_VID3_SIZE 0x00000000 DISPC_DISPC_DEFAULT_COLOR2 0x00000000 DISPC_DISPC_TRANS_COLOR2 0x00000000 DISPC_DISPC_CPR2_COEF_B 0x00000000 DISPC_DISPC_CPR2_COEF_G 0x00000000 DISPC_DISPC_CPR2_COEF_R 0x00000000 DISPC_DISPC_DATA2_CYCLE1 0x00000000 DISPC_DISPC_DATA2_CYCLE2 0x00000000 DISPC_DISPC_DATA2_CYCLE3 0x00000000 DISPC_DISPC_SIZE_LCD2 0x00000000 DISPC_DISPC_TIMING_H2 0x00000000 DISPC_DISPC_TIMING_V2 0x00000000 DISPC_DISPC_POL_FREQ2 0x00000000 DISPC_DISPC_DIVISOR2 0x00040001 DISPC_DISPC_WB_ACCU_j_0 0x00000000 DISPC_DISPC_WB_ACCU_j_1 0x00000000 DISPC_DISPC_WB_BA_j_0 0x00000000 DISPC_DISPC_WB_BA_j_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_H_i_7 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV_i_7 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_V_i_7 0x00000000 DISPC_DISPC_WB_ATTRIBUTES 0x00008000 DISPC_DISPC_WB_CONV_COEF0 0x00000000 DISPC_DISPC_WB_CONV_COEF1 0x00000000 DISPC_DISPC_WB_CONV_COEF2 0x00000000 DISPC_DISPC_WB_CONV_COEF3 0x00000000 DISPC_DISPC_WB_CONV_COEF4 0x00000000 DISPC_DISPC_WB_BUF_SIZE_STATUS 0x00000800 DISPC_DISPC_WB_BUF_THRESHOLD 0x07FF07F8 DISPC_DISPC_WB_FIR 0x04000400 DISPC_DISPC_WB_PICTURE_SIZE 0x00000000 DISPC_DISPC_WB_PIXEL_INC 0x00000001 DISPC_DISPC_WB_ROW_INC 0x00000001 DISPC_DISPC_WB_SIZE 0x00000000 DISPC_DISPC_VID1_BA_UV_j_0 0x00000000 DISPC_DISPC_VID1_BA_UV_j_1 0x00000000 DISPC_DISPC_VID2_BA_UV_j_0 0x00000000 DISPC_DISPC_VID2_BA_UV_j_1 0x00000000 DISPC_DISPC_VID3_BA_UV_j_0 0x00000000 DISPC_DISPC_VID3_BA_UV_j_1 0x00000000 DISPC_DISPC_WB_BA_UV_j_0 0x00000000 DISPC_DISPC_WB_BA_UV_j_1 0x00000000 DISPC_DISPC_CONFIG2 0x00000000 DISPC_DISPC_VID1_ATTRIBUTES2 0x00000000 DISPC_DISPC_VID2_ATTRIBUTES2 0x00000000 DISPC_DISPC_VID3_ATTRIBUTES2 0x00000000 DISPC_DISPC_GAMMA_TABLE0 0x00000000 DISPC_DISPC_GAMMA_TABLE1 0x00000000 DISPC_DISPC_GAMMA_TABLE2 0x00000000 DISPC_DISPC_VID1_FIR2 0x04000200 DISPC_DISPC_VID1_ACCU2_j_0 0x00000000 DISPC_DISPC_VID1_ACCU2_j_1 0x00000000 DISPC_DISPC_VID1_FIR_COEF_H2_i_0 0x00800000 DISPC_DISPC_VID1_FIR_COEF_H2_i_1 0x0E7DF601 DISPC_DISPC_VID1_FIR_COEF_H2_i_2 0x2172F102 DISPC_DISPC_VID1_FIR_COEF_H2_i_3 0x3762F001 DISPC_DISPC_VID1_FIR_COEF_H2_i_4 0xF24E4EF2 DISPC_DISPC_VID1_FIR_COEF_H2_i_5 0xF06237F6 DISPC_DISPC_VID1_FIR_COEF_H2_i_6 0xF17221FA DISPC_DISPC_VID1_FIR_COEF_H2_i_7 0xF67D0EFE DISPC_DISPC_VID1_FIR_COEF_HV2_i_0 0x00800000 DISPC_DISPC_VID1_FIR_COEF_HV2_i_1 0x0E7DF6FE DISPC_DISPC_VID1_FIR_COEF_HV2_i_2 0x2172F1FA DISPC_DISPC_VID1_FIR_COEF_HV2_i_3 0x3762F0F6 DISPC_DISPC_VID1_FIR_COEF_HV2_i_4 0xF24E4E00 DISPC_DISPC_VID1_FIR_COEF_HV2_i_5 0xF0623701 DISPC_DISPC_VID1_FIR_COEF_HV2_i_6 0xF1722102 DISPC_DISPC_VID1_FIR_COEF_HV2_i_7 0xF67D0E01 DISPC_DISPC_VID1_FIR_COEF_V2_i_0 0x00000000 DISPC_DISPC_VID1_FIR_COEF_V2_i_1 0x0000FE01 DISPC_DISPC_VID1_FIR_COEF_V2_i_2 0x0000FA02 DISPC_DISPC_VID1_FIR_COEF_V2_i_3 0x0000F601 DISPC_DISPC_VID1_FIR_COEF_V2_i_4 0x000000F2 DISPC_DISPC_VID1_FIR_COEF_V2_i_5 0x000001F6 DISPC_DISPC_VID1_FIR_COEF_V2_i_6 0x000002FA DISPC_DISPC_VID1_FIR_COEF_V2_i_7 0x000001FE DISPC_DISPC_VID2_FIR2 0x04000400 DISPC_DISPC_VID2_ACCU2_j_0 0x00000000 DISPC_DISPC_VID2_ACCU2_j_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_H2_i_7 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_HV2_i_7 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_0 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_1 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_2 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_3 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_4 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_5 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_6 0x00000000 DISPC_DISPC_VID2_FIR_COEF_V2_i_7 0x00000000 DISPC_DISPC_VID3_FIR2 0x04000400 DISPC_DISPC_VID3_ACCU2_j_0 0x00000000 DISPC_DISPC_VID3_ACCU2_j_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_H2_i_7 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_HV2_i_7 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_0 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_1 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_2 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_3 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_4 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_5 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_6 0x00000000 DISPC_DISPC_VID3_FIR_COEF_V2_i_7 0x00000000 DISPC_DISPC_WB_FIR2 0x04000400 DISPC_DISPC_WB_ACCU2_j_0 0x00000000 DISPC_DISPC_WB_ACCU2_j_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_H2_i_7 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_HV2_i_7 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_0 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_1 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_2 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_3 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_4 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_5 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_6 0x00000000 DISPC_DISPC_WB_FIR_COEF_V2_i_7 0x00000000 DISPC_DISPC_GLOBAL_BUFFER 0x246D2240 DISPC_DISPC_DIVISOR 0x00010001 DISPC_DISPC_WB_ATTRIBUTES2 0x00000000 DISPC_DISPC_DEFAULT_COLOR3 0x00000000 DISPC_DISPC_TRANS_COLOR3 0x00000000 DISPC_DISPC_CPR3_COEF_B 0x00000000 DISPC_DISPC_CPR3_COEF_G 0x00000000 DISPC_DISPC_CPR3_COEF_R 0x00000000 DISPC_DISPC_DATA3_CYCLE1 0x00000000 DISPC_DISPC_DATA3_CYCLE2 0x00000000 DISPC_DISPC_DATA3_CYCLE3 0x00000000 DISPC_DISPC_SIZE_LCD3 0x00000000 DISPC_DISPC_DIVISOR3 0x00040001 DISPC_DISPC_POL_FREQ3 0x00000000 DISPC_DISPC_TIMING_H3 0x00000000 DISPC_DISPC_TIMING_V3 0x00000000 DISPC_DISPC_CONTROL3 0x00000300 DISPC_DISPC_CONFIG3 0x00000000 DISPC_DISPC_GAMMA_TABLE3 0x00000000 DISPC_DISPC_BA0_FLIPIMMEDIATE_EN 0x00000000 DISPC_DISABLE_MSTANDBY_ENHANCEMENT 0x00000001 DISPC_DISPC_GLOBAL_MFLAG_ATTRIBUTE 0x00000000 DISPC_DISPC_GFX_MFLAG_THRESHOLD 0x00000000 DISPC_DISPC_VID1_MFLAG_THRESHOLD 0x00000000 DISPC_DISPC_VID2_MFLAG_THRESHOLD 0x00000000 DISPC_DISPC_VID3_MFLAG_THRESHOLD 0x00000000 DISPC_DISPC_WB_MFLAG_THRESHOLD 0x00000000

谢谢