主题中讨论的其他器件:DRA829、 DRA821

如何在 RTOS/SBL 和 Linux/SPL 引导流程上更改 DRA821/DRA829中 A72和主 R5F 内核的频率? 并在 Uboot 中禁用一个 A72内核?

此致

葡萄园

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在 SBL 引导流程中更改频率:

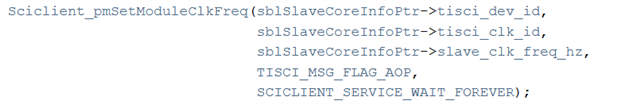

使用 RTOS/SBL 引导流程、用户可以使用 API Sciclient_pmSetModuleClkFreq ()来更改主 R5F 内核的频率、然后 API 会设置底层的 TI SCI 消息参数。

在 SBL 代码中使用所需的时钟频率(在我们引导之前)设置处理器引导内核的示例:ti/boot/sbl/soc/k3/sbl_slave_core_boot.c

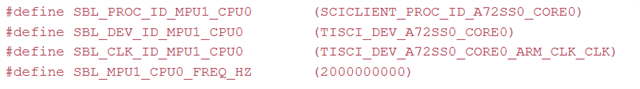

要使用此 Sciclient API、请查找需要配置的内核的 dev ID (这不是主机 ID)、然后查找对应的主处理器时钟的相关 CLK ID、然后设置 clk 频率。

每个内核的示例值显示在这里的另一个文件中(这里是 A72内核值的示例):TI/BOOT/SBL/SoC/K3/sbl_soc_cfg.h

在 Uboot/SPL 引导流程中更改频率:

要将 A72的频率更改为400MHz、请使用以下 Uboot 补丁

e2e.ti.com/.../u_2D00_boot_2D00_patch_2D00_a72_2D00_freq_2D00_400mhz.patch

要在 SPL 引导加载程序中更改主 R5F 内核的频率、请使用以下补丁修改 DTS 以更改 R5F 节点中的频率

在 Uboot 中禁用 A72内核:

要禁用内核、请在 Uboot 中使用以下补丁

e2e.ti.com/.../disabling_5F00_a72_5F00_core_5F00_uboot.patch

此致

葡萄园