Thread 中讨论的其他器件:SYSBIOS、

您好!

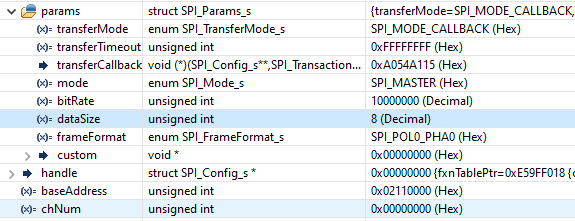

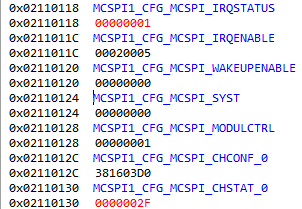

我正在 J20连接器中测试 AM65X IDK 的 SPI。 它是 MCSPI1。 我的代码正在 R5F 内核上运行、在对 驱动程序表进行少量更改后、我可以发送和接收。

我想测试 DMA、我的问题是: 是否可以通过 MCU 域的 DMA 访问主域中的外设?

我找到 pdk_jacinto_07_00_00\packages/ti\drv\spi\examples\mcspi_slavemode\示例、并且能够成功运行它、但它处理内部连接的 SPI 端口、而无需域交叉。

此致、

卡尔曼