Thread 中讨论的其他器件: OMAPL138

工具/软件:Code Composer Studio

您好、先生、

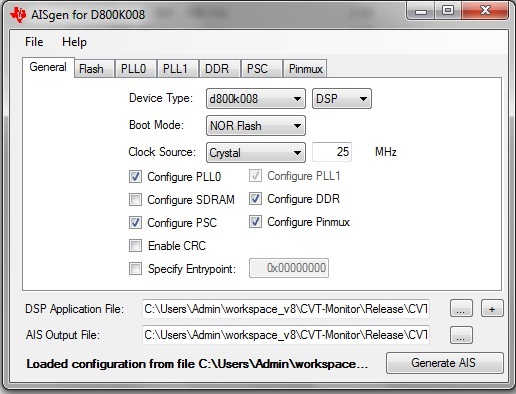

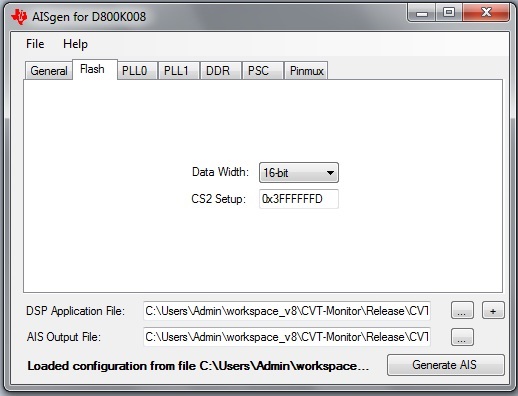

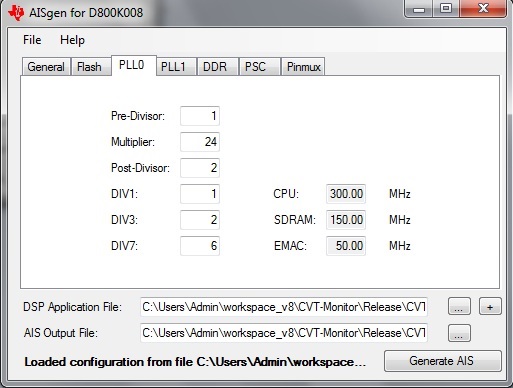

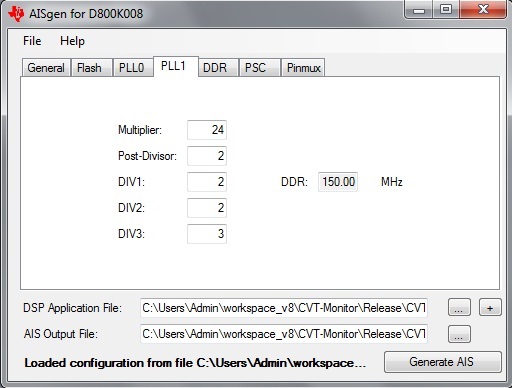

我使用的是 TMS320C6748 DSP 和外部 NOR 闪存。

实际上、在.cmd 文件 DSPL2RAM 中、我使用的是从 NOR 闪存引导、当我在.cmd 中更改为 DDR2时、它不会引导。

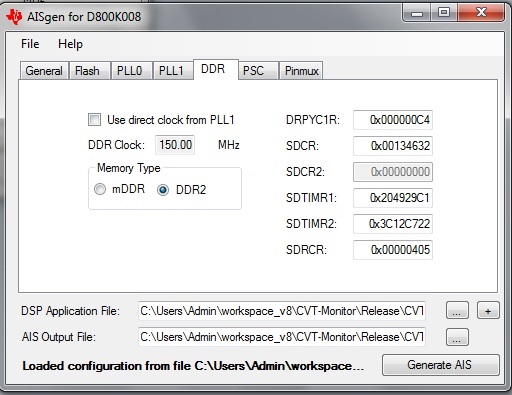

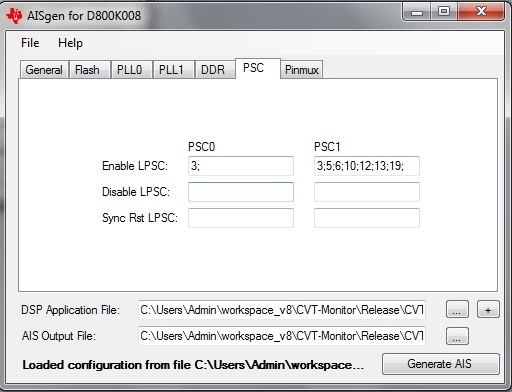

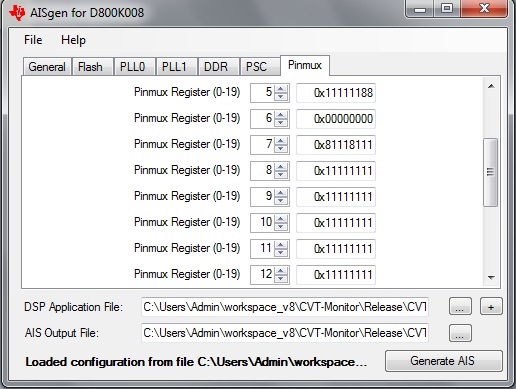

在 AIS Gen 中、所有设置均已正确给出、请您能给我一些建议。

下面我附加 AIS Gen 设置映像和 (在调试模式下使用 DDR2工作正常的任何内容) OMAPL138_LCDK-GEL 连接。

我也在连接我的 GEL (OMAPL138_LCDK)文件 SIR、

#define PLL0_BASE 0x01C11000 /*系统 PLL 基地址*/

#define PLL0_PID *(无符号整型*)(PLL0_BASE + 0x00)/* PID*/

#define PLL0_RSTYPE *(无符号 int*)(PLL0_BASE + 0xE4)/*复位类型状态寄存器*/

#define PLL0_PLLCTL *(无符号 int*)(PLL0_BASE + 0x100)/* PLL 控制寄存器*/

#define PLL0_OCSEL *(无符号 int*)(PLL0_BASE + 0x104)/* OBSCLK 选择寄存器*/

#define PLL0_SECCTL *(无符号 int*)(PLL0_BASE + 0x108)/* PLL 次级控制寄存器*/

#define PLL0_PLLM *(unsigned int*)(PLL0_BASE + 0x110)/* PLL 乘法器*/

#define PLL0_PREDIV *(unsigned int*)(PLL0_BASE + 0x114)/*预分频器*/

#define PLL0_PLLDIV1 *(无符号 int*)(PLL0_BASE + 0x118)/* Divider-1*/

#define PLL0_PLLDIV2 *(unsigned int*)(PLL0_BASE + 0x11C)/* Divider-2*/

#define PLL0_PLLDIV3 *(无符号 int*)(PLL0_BASE + 0x120)/* Divider-3*/

#define PLL0_OSCDIV1 *(无符号 int*)(PLL0_BASE + 0x124)/*振荡器分频器*/

#define PLL0_POSTDIV *(无符号 int*)(PLL0_BASE + 0x128)/* Post Divider*/

#define PLL0_BPDIV *(无符号 int*)(PLL0_BASE + 0x12C)/*旁路分频器*/

#define PLL0_WAKEUP *(无符号整型*)(PLL0_BASE + 0x130)/*唤醒寄存器*/

#define PLL0_PLLCMD *(无符号整型*)(PLL0_BASE + 0x138)/*命令寄存器*/

#define PLL0_PLLSTAT *(无符号整型*)(PLL0_BASE + 0x13C)/*状态寄存器*/

#define PLL0_ALNCTL *(无符号整型*)(PLL0_BASE + 0x140)/*时钟对齐控制寄存器*/

#define PLL0_DCHANGE *(unsigned int*)(PLL0_BASE + 0x144)/* PLLDIV Ratio Chnage status*/

#define PLL0_CKEN *(无符号整型*)(PLL0_BASE + 0x148)/*时钟启用寄存器*/

#define PLL0_CKSTAT *(无符号整型*)(PLL0_BASE + 0x14C)/*时钟状态寄存器*/

#define PLL0_SYSTAT *(无符号整型*)(PLL0_BASE + 0x150)/* SYSCLK 状态寄存器*/

#define PLL0_PLLDIV4 *(无符号 int*)(PLL0_BASE + 0x160)/*除法器4*/

#define PLL0_PLLDIV5 *(无符号整型*)(PLL0_BASE + 0x164)/*除法器5*/

#define PLL0_PLLDIV6 *(无符号整型*)(PLL0_BASE + 0x168)/*除法器6*/

#define PLL0_PLLDIV7 *(无符号 int*)(PLL0_BASE + 0x16C)/*除法器7*/

#define PLL0_PLLDIV8 *(无符号整型*)(PLL0_BASE + 0x170)/*除法器8*/

#define PLL0_PLLDIV9 *(无符号整型*)(PLL0_BASE + 0x174)/*除法器9*/

#define PLL0_PLLDIV10 *(无符号 int*)(PLL0_BASE + 0x178)/*除法器10*/

#define PLL0_PLLDIV11 *(无符号 int*)(PLL0_BASE + 0x17C)/*除法器11*/

#define PLL0_PLLDIV12 *(无符号整型*)(PLL0_BASE + 0x180)/*除法器12*/

#define PLL0_PLLDIV13 *(无符号 int*)(PLL0_BASE + 0x184)/*除法器13*/

#define PLL0_PLLDIV14 *(无符号 int*)(PLL0_BASE + 0x188)/*除法器14*/

#define PLL0_PLLDIV15 *(无符号 int*)(PLL0_BASE + 0x18C)/*除法器15*/

#define PLL0_PLLDIV16 *(无符号 int*)(PLL0_BASE + 0x190)/*除法器16*/

#define PLL1_BASE 0x01E1A000 /*系统 PLL1基址*/

#define PLL1_PID *(无符号整型*)(PLL1_BASE + 0x00)/* PID*/

#define PLL1_RSTYPE *(unsigned int*)(PLL1_base + 0xE4)/*复位类型状态寄存器*/

#define PLL1_PLLCTL *(无符号 int*)(PLL1_base + 0x100)/* PLL 控制寄存器*/

#define PLL1_OCSEL *(无符号 int*)(PLL1_base + 0x104)/* OBSCLK 选择寄存器*/

#define PLL1_SECCTL *(无符号 int*)(PLL1_BASE + 0x108)/* PLL 次级控制寄存器*/

#define PLL1_PLLM *(unsigned int*)(PLL1_base + 0x110)/* PLL 乘法器*/

#define PLL1_PREDIV *(unsigned int*)(PLL1_base + 0x114)/*预分频器*/

#define PLL1_PLLDIV1 *(无符号 int*)(PLL1_BASE + 0x118)/*分频器-1*/

#define PLL1_PLLDIV2 *(无符号 int*)(PLL1_BASE + 0x11C)/*分频器-2*/

#define PLL1_PLLDIV3 *(无符号 int*)(PLL1_BASE + 0x120)/*分频器-3*/

#define PLL1_OSCDIV1 *(无符号 int*)(PLL1_BASE + 0x124)/*振荡器分频器*/

#define PLL1_POSTDIV *(unsigned int*)(PLL1_base + 0x128)/* Post Divider*/

#define PLL1_BPDIV *(unsigned int*)(PLL1_base + 0x12C)/*旁路分频器*/

#define PLL1_WAKEUP *(无符号整型*)(PLL1_BASE + 0x130)/*唤醒寄存器*/

#define PLL1_PLLCMD *(unsigned int*)(PLL1_base + 0x138)/*命令注册*

#define PLL1_PLLSTAT *(无符号整型*)(PLL1_BASE + 0x13C)/*状态寄存器*/

#define PLL1_ALNCTL *(无符号 int*)(PLL1_BASE + 0x140)/*时钟对齐控制寄存器*/

#define PLL1_DCHANGE *(unsigned int*)(PLL1_base + 0x144)/* PLLDIV 比率填充状态*/

#define PLL1_CKEN *(无符号整型*)(PLL1_BASE + 0x148)/*时钟启用寄存器*/

#define PLL1_CKSTAT *(无符号整型*)(PLL1_BASE + 0x14C)/*时钟状态寄存器*/

#define PLL1_SYSTAT *(unsigned int*)(PLL1_base + 0x150)/* SYSCLK 状态寄存器*/

#define PLL1_PLLDIV4 *(无符号 int*)(PLL1_BASE + 0x160)/*除法器4*/

#define PLL1_PLLDIV5 *(无符号 int*)(PLL1_BASE + 0x164)/*除法器5*/

#define PLL1_PLLDIV6 *(无符号 int*)(PLL1_BASE + 0x168)/*除法器6*/

#define PLL1_PLLDIV7 *(无符号 int*)(PLL1_BASE + 0x16C)/*除法器7*/

#define PLL1_PLLDIV8 *(无符号 int*)(PLL1_BASE + 0x170)/*除法器8*/

#define PLL1_PLLDIV9 *(无符号 int*)(PLL1_BASE + 0x174)/*除法器9*/

#define PLL1_PLLDIV10 *(无符号 int*)(PLL1_BASE + 0x178)/*除法器10*/

#define PLL1_PLLDIV11 *(无符号 int*)(PLL1_BASE + 0x17C)/*除法器11*/

#define PLL1_PLLDIV12 *(无符号 int*)(PLL1_BASE + 0x180)/*除法器12*/

#define PLL1_PLLDIV13 *(无符号 int*)(PLL1_BASE + 0x184)/*除法器13*/

#define PLL1_PLLDIV14 *(无符号 int*)(PLL1_BASE + 0x188)/*除法器14*/

#define PLL1_PLLDIV15 *(无符号 int*)(PLL1_BASE + 0x18C)/*除法器15*/

#define PLL1_PLLDIV16 *(无符号 int*)(PLL1_BASE + 0x190)/*除法器16*/

/*PSC 模块相关寄存器*/

#define PSC0_BASE 0x01C10000

#define PSC1_base 0x01E27000

#define PSC0_MDCTL (PSC0_BASE+0xA00)

#define PSC0_mdstat (PSC0_BASE+0x800)

#define PSC0_PTCMD *(无符号整型*)(PSC0_BASE + 0x120)

#define PSC0_PTSTAT *(无符号整型*)(PSC0_BASE + 0x128)

#define PSC1_MDCTL (PSC1_BASE+0xA00)

#define PSC1_mdstat (PSC1_BASE+0x800)

#define PSC1_PTCMD *(无符号整型*)(PSC1_BASE + 0x120)

#define PSC1_PTSTAT *(无符号整型*)(PSC1_BASE + 0x128)

#define PSC_TIMEOUT 200 //用户可以优化此值

#define LPSC_EDMA_cC0

#define LPSC_EDMA_TC0 1.

#define LPSC_EDMA_TC1 2.

#define LPSC_EMIFA 3/* PSC0*/

#define LPSC SPI0 4/* PSC0*/

#define LPSC MMCSD0 5/* PSC0*/

#define LPSC_ARM_AINTC 6.

#define LPSC ARM_RAMROM 7/* PSC0*/

//未使用 LPSC #8

#define LPSC UART0 9 /* PSC0*/

#define LPSC_SCR0 10.

#define LPSC_SCR1 11.

#define LPSC_SCR2 12.

//未使用 LPSC #13

#define LPSC ARM 14 /* PSC0*/

#define LPSC_DSP 15/* PSC0*/

#define LPSC_EDMA_CC1 0

#define LPSC_USB20 1/* PSC1*/

#define LPSC USB11 2 /* PSC1*/

#define LPSC_GPIO 3/*PSC1*/

#define LPSC UHPI 4/* PSC1*/

#define LPSC_EMAC 5/* PSC1*/

#define LPSC_DDR 6/* PSC1*/

#define LPSC_McASP0 7/*PSC1*/

#define LPSC_SATA 8/* PSC1*/

#define LPSC VPIF 9 /*PSC1*/

#define LPSC_SPI1 10/* PSC1*/

#define LPSC_I2C1 11/* PSC1*/

#define LPSC UART1 12/* PSC1*/

#define LPSC UART2 13 /* PSC1*/

#define LPSC MCBSP0 14 /* PSC1*/

#define LPSC MCBSP1 15/* PSC1*/

#define LPSC_LCDC 16/* PSC1*/

#define LPSC ePWM 17 /*PSC1*/

#define LPSC MMCSD1 18.

#define LPSC UPP 19.

#define LPSC_ECAP 20.

#define LPSC_EDMA_TC2 21.

//未使用 LPSC #22-23

#define LPSC_SCR_F0 24.

#define LPSC_SCR_F1 25.

#define LPSC_SCR_F2 26.

#define LPSC_SCR_F6 27.

#define LPSC_SCR_F7 28.

#define LPSC_SCR_F8 29.

#define LPSC_BR_F7 30.

#define LPSC shared_RAM 31.

/*DDR MMR 声明*/

#define VTPIO_CTL *(unsigned int*)(0x01E2C000)// VTPIO_CTL 寄存器

#define EMIFDDR_SDRAM_CFG 0xB0000000

#define EMIFDDR_REVID *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x00)//EMIF 模块 ID 和修订寄存器

#define EMIFDDR_SDRSTAT *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x04)//SDRAM 状态寄存器

#define EMIFDDR_SDCR *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x08)//SDRAM 组配置寄存器

#define EMIFDDR_SDRCR *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x0C)//SDRAM 刷新控制寄存器

#define EMIFDDR_SDTIMR1 *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x10)//SDRAM 时序寄存器1

#define EMIFDDR_SDTIMR2 *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x14)//SDRAM 时序寄存器2

#define EMIFDDR_SDCR2 *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x1C)//SDRAM 配置寄存器2

#define EMIFDDR_PBBPR *(无符号整型*)(EMIFDDR_SDRAM_CFG + 0x20)//VBUSM 突发优先级寄存器

#define EMIFDDR_VBUSMCFG1 *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x28)//VBUSM 配置 Value1寄存器

#define EMIFDDR_VBUSMCFG2 *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0x2C)//VBUSM 配置 Value2寄存器

#define EMIFDDR_IRR *(无符号整型*)(EMIFDDR_SDRAM_CFG + 0xC0)//中断原始寄存器

#define EMIFDDR_IMR *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0xC4)//中断屏蔽寄存器

#define EMIFDDR_IMSR *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0xC8)//中断屏蔽设置寄存器

#define EMIFDDR_IMCR *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0xCC)//中断屏蔽清除寄存器

#define DDRPHYREV *(无符号 int*)(EMIFDDR_SDRAM_CFG + 0xE0)//DDR PHY ID 和修订寄存器

#define DRPYC1R *(无符号整型*)(EMIFDDR_SDRAM_CFG + 0xE4)//DDR PHY 控制1寄存器

#define DDR2 0 //不要更改此值

#define mDDR 1 //不要更改此值

#define VTP 超时200 //用户可以优化该值

#define DDR_DEBUG 0 //将其设置为"1"以对具有更多时序可宽延时间的 DDR 进行编程

#define EMIFDDR_BASE_ADDR 0xC0000000

#define EMIFA_BASE_ADDR 0x40000000

#define EMIFA_CS2_base_ADDR 0x60000000

#define EMIFA_CS3_BASE_ADDR 0x62000000

#define EMIFA_CS4_BASE_ADDR 0x64000000

#define EMIFA_CS5_BASE_ADDR 0x66000000

/*EMIF2.5 MMR 宣言*/

#define EMIFA 0x68000000

#define EMIFA_AWAITCFG *(无符号 int*)(EMIFA + 0x04)

#define EMIFA_SDCFG *(无符号 int*)(EMIFA + 0x08)

#define EMIFA_SDREF *(无符号 int*)(EMIFA + 0x0C)

#define EMIFA_ACFG2 *(无符号 int*)(EMIFA + 0x10)//异 步 BANK1配置寄存器

#define EMIFA_ACFG3 *(无符号 int*)(EMIFA + 0x14)//异 步 Bank2配置寄存器

#define EMIFA_ACFG4 *(无符号 int*)(EMIFA + 0x18)//异 步 Bank3配置寄存器

#define EMIFA_ACFG5 *(无符号 int*)(EMIFA + 0x1C)//异 步 Bank4配置寄存器

#define EMIFA_SDTIM *(无符号 int*)(EMIFA + 0x20)//SDRAM 时序寄存器

#define EMIFA_SRPD *(无符号 int*)(EMIFA + 0x3C)

#define EMIFA_NANDFCR *(无符号 int*)(EMIFA + 0x60)

/*GPIO MMR*/

#define GPIO_REG_BASE (0x01E26000)

#define GPIO_Bank_OFFSET (0x28)

#define GPIO_DAT_OFFSET (0x04)

#define GPIO_SET_OFFSET (0x08)

#define GPIO_CLR_OFFSET (0x0C)

#define GPIO_BINTEN *(无符号 int*)(GPIO_REG_BASE + 0x08)

#define GPIO_BANK01_BASE (GPIO_REG_BASE + 0x10)

#define GPIO_BANK23_BASE (GPIO_BANK01_BASE + GPIO_BANK_OFFSET)

#define GPIO_BANK45_BASE (GPIO_BANK23_BASE + GPIO_BANK_OFFSET)

#define GPIO_BANK67_BASE (GPIO_BANK45_BASE + GPIO_BANK_OFFSET)

#define GPIO_BANK8_BASE (GPIO_BANK67_BASE + GPIO_BANK_OFFSET)

#define GPIO_BANK23_DIR *(无符号 int*)(GPIO_BANK23_BASE)

#define GPIO_BANK23_DAT *(无符号 int*)(GPIO_BANK23_BASE + GPIO_DAT_OFFSET)

#define GPIO_BANK23_SET *(无符号 int*)(GPIO_BANK23_BASE + GPIO_SET_OFFSET)

#define GPIO_BANK23_CLR *(无符号 int*)(GPIO_BANK23_BASE + GPIO_CLR_OFFSET)

/*系统 MMR 声明*/

#define SYS_base 0x01C14000

#define HOST0CFG *(无符号 int*)(SYS_BASE + 0x040)//ARM HOST0CFG

#define KICK0R *(无符号 int*)(SYS_BASE + 0x038)

#define KICK1R *(无符号 int*)(SYS_BASE + 0x03c)

#define PINMUX0 *(无符号 int*)(SYS_BASE + 0x120)//PINMUX0

#define PINMUX1 *(unsigned int*)(SYS_base + 0x124)//PINMUX1

#define PINMUX2 *(无符号 int*)(SYS_BASE + 0x128)//PINMUX2

#define PINMUX3 *(无符号 int*)(SYS_BASE + 0x12C)//PINMUX3

#define PINMUX4 *(无符号 int*)(SYS_BASE + 0x130)//PINMUX4

#define PINMUX5 *(无符号 int*)(SYS_BASE + 0x134)//PINMUX5

#define PINMUX6 *(无符号 int*)(SYS_BASE + 0x138)//PINMUX6

#define PINMUX7 *(无符号 int*)(SYS_BASE + 0x13C)//PINMUX7

#define PINMUX8 *(无符号 int*)(SYS_BASE + 0x140)//PINMUX8

#define PINMUX9 *(无符号 int*)(SYS_BASE + 0x144)//PINMUX9

#define PINMUX10 *(无符号 int*)(SYS_BASE + 0x148)//PINMUX10

#define PINMUX11 *(无符号 int*)(SYS_BASE + 0x14C)//PINMUX11

#define PINMUX12 *(无符号 int*)(SYS_BASE + 0x150)//PINMUX12

#define PINMUX13 *(无符号 int*)(SYS_BASE + 0x154)//PINMUX13

#define PINMUX14 *(无符号 int*)(SYS_BASE + 0x158)//PINMUX14

#define PINMUX15 *(无符号 int*)(SYS_BASE + 0x15C)//PINMUX15

#define PINMUX16 *(无符号 int*)(SYS_BASE + 0x160)//PINMUX16

#define PINMUX17 *(unsigned int*)(SYS_base + 0x164)//PINMUX17

#define PINMUX18 *(无符号 int*)(SYS_BASE + 0x168)//PINMUX18

#define PINMUX19 *(无符号 int*)(SYS_BASE + 0x16C)//PINMUX19

#define CFGCHIP0 *(无符号整型*)(SYS_BASE + 0x17C)

#define CFGCHIP2 *(unsigned int*)(SYS_base + 0x184)

#define CFGCHIP3 *(unsigned int*)(SYS_base + 0x188)

#define PD0 /*Power Domain-0*/

#define PD1 /*电源域-1*/

#define PLLEN_MUX_SWITCH 4.

#define PLL_LOCK_TIME_CNT 2400

#define PLL_稳定化 时间2000

#define PLL_RESET_TIME_CNT 200

OnTargetConnect()

{

GEL_TextOut ("\tTarget 已连接。\n"、"输出"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

CLEAR_Memory_Map();

Setup_Memory_Map();

PSC_all_ON();

core_300MHz_mDDR_150MHz ();

WAKE_DSP();

}

菜单项"唤醒内核"

热菜单 Wake_DSP()

{

PSC0_LPSC enableCore (1、LPSC DSP);

GEL_TextOut ("\tDSP 唤醒完成。\n"、"输出"、1、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

菜单项"OMAP-L138 内存映射"

/*---------------------------------------------- *

**

* CLEAR_Memory_Map()*

*清除内存映射*

**

******************************************************************************************************* *

热菜单 CLEAR_Memory_Map()

{

GEL_MapOff ();

GEL_MapReset();

GEL_TextOut ("\tMemory Map Cleared。\n"、"Output"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Setup_Memory_Map()

{

GEL_MapOn();

GEL_MapReset();

/* arm */

GEL_MapAddStr (0xFFFD0000、0、0x00010000、"R|W|AS4"、0); // ARM 本地 ROM

GEL_MapAddStr (0xFFFEE000、0、0x00001000、"R|W|AS4"、0); // ARM INTC

GEL_MapAddStr (0xFFFFFF0000、0、0x00002000、"R|W|AS4"、0); // ARM 本地 RAM

GEL_MapAddStr (0x01BC0000、0、0x00001000、"R|W|AS4"、0); // ARM ETB 内存

GEL_MapAddStr (0x01BC1000、0、0x00000800、"R|W|AS4"、0); // ARM ETB 寄存器

GEL_MapAddStr (0x01BC1800、0、0x00000100、"R|W|AS4"、0); //手臂冰上撑

/* DSP */

GEL_MapAddStr (0x00700000、0、0x00100000、"R|W|AS4"、0); // DSP L2 ROM

GEL_MapAddStr (0x00800000、0、0x00040000、"R|W|AS4"、0); // DSP L2 RAM

GEL_MapAddStr (0x00E00000、0、0x00008000、"R|W|AS4"、0); // DSP L1P RAM

GEL_MapAddStr (0x00F00000、0、0x00008000、"R|W|AS4"、0); // DSP L1D RAM

GEL_MapAddStr (0x01800000、0、0x00010000、"R|W|AS4"、0); // DSP 中断控制器

GEL_MapAddStr (0x01810000、0、0x00001000、"R|W|AS4"、0); // DSP 断电控制器

GEL_MapAddStr (0x01811000、0、0x00001000、"R|W|AS4"、0); // DSP 安全 ID

GEL_MapAddStr (0x01812000、0、0x00008000、"R|W|AS4"、0); // DSP 修订 ID

GEL_MapAddStr (0x01820000、0、0x00010000、"R|W|AS4"、0); // DSP EMC

GEL_MapAddStr (0x01830000、0、0x00010000、"R|W|AS4"、0); // DSP 内部保留

GEL_MapAddStr (0x01840000、0、0x00010000、"R|W|AS4"、0); // DSP 内存系统

GEL_MapAddStr (0x11700000、0、0x00100000、"R|W|AS4"、0); // DSP L2 ROM (镜像)

GEL_MapAddStr (0x11800000、0、0x00040000、"R|W|AS4"、0); // DSP L2 RAM (镜像)

GEL_MapAddStr (0x11E00000、0、0x00008000、"R|W|AS4"、0); // DSP L1P RAM (镜像)

GEL_MapAddStr (0x11F00000、0、0x00008000、"R|W|AS4"、0); // DSP L1D RAM (镜像)

/*共享 RAM */

GEL_MapAddStr (0x80000000、0、0x00020000、"R|W|AS4"、0); //共享 RAM

/* EMIFA */

GEL_MapAddStr (0x40000000、0、0x20000000、"R|W|AS4"、0); // EMIFA SDRAM 数据

GEL_MapAddStr (0x60000000、0、0x02000000、"R|W|AS4"、0); // EMIFA CS2

GEL_MapAddStr (0x62000000、0、0x02000000、"R|W|AS4"、0); // EMIFA CS3

GEL_MapAddStr (0x64000000、0、0x02000000、"R|W|AS4"、0); // EMIFA CS4

GEL_MapAddStr (0x66000000、0、0x02000000、"R|W|AS4"、0); // EMIFA CS5

GEL_MapAddStr (0x68000000、0、0x00008000、"R|W|AS4"、0); // EMIFA 控制

/* DDR */

GEL_MapAddStr (0xB0000000、0、0x00008000、"R|W|AS4"、0); // DDR 控制

GEL_MapAddStr (0xC0000000、0、0x20000000、"R|W|AS4"、0); // DDR 数据

/*外设*/

GEL_MapAddStr (0x01C00000、0、0x00008000、"R|W|AS4"、0); // TPCC0

GEL_MapAddStr (0x01C08000、0、0x00000400、"R|W|AS4"、0); // TPTC0

GEL_MapAddStr (0x01C08400、0、0x00000400、"R|W|AS4"、0); // TPTC1

GEL_MapAddStr (0x01C10000、0、0x00001000、"R|W|AS4"、0); // PSC 0

GEL_MapAddStr (0x01C11000、0、0x00001000、"R|W|AS4"、0); // PLL 控制器0

GEL_MapAddStr (0x01C12000、0、0x00001000、"R|W|AS4"、0); //密钥管理器

GEL_MapAddStr (0x01C13000、0、0x00001000、"R|W|AS4"、0); // Secco

GEL_MapAddStr (0x01C14000、0、0x00001000、"R|W|AS4"、0); // SysConfig

GEL_MapAddStr (0x01C16000、0、0x00001000、"R|W|AS4"、0); // IOPU 0

GEL_MapAddStr (0x01C17000、0、0x00001000、"R|W|AS4"、0); // IOPU 2

GEL_MapAddStr (0x01C20000、0、0x00001000、"R|W|AS4"、0); // Timer64P 0

GEL_MapAddStr (0x01C21000、0、0x00001000、"R|W|AS4"、0); // Timer64P 1.

GEL_MapAddStr (0x01C22000、0、0x00001000、"R|W|AS4"、0); // I2C 0

GEL_MapAddStr (0x01C23000、0、0x00001000、"R|W|AS4"、0); // RTC

GEL_MapAddStr (0x01C24000、0、0x00001000、"R|W|AS4"、0); // IOPU 1

GEL_MapAddStr (0x01C30000、0、0x00000200、"R|W|AS4"、0); // PRU 数据 RAM 0

GEL_MapAddStr (0x01C32000、0、0x00000200、"R|W|AS4"、0); // PRU 数据 RAM 1.

GEL_MapAddStr (0x01C34000、0、0x00004000、"R|W|AS4"、0); // PRU 控制寄存器

GEL_MapAddStr (0x01C38000、0、0x00001000、"R|W|AS4"、0); // PRU 0配置存储器

GEL_MapAddStr (0x01C3C000、0、0x00001000、"R|W|AS4"、0); // PRU 1配置存储器

GEL_MapAddStr (0x01C40000、0、0x00001000、"R|W|AS4"、0); // MMC/SD 0

GEL_MapAddStr (0x01C41000、0、0x00001000、"R|W|AS4"、0); // SPI 0

GEL_MapAddStr (0x01C42000、0、0x00001000、"R|W|AS4"、0); // UART 0

GEL_MapAddStr (0x01C43000、0、0x00001000、"R|W|AS4"、0); // MPU 0

GEL_MapAddStr (0x01D00000、0、0x00001000、"R|W|AS4"、0); // McASP 0控制

GEL_MapAddStr (0x01D01000、0、0x00001000、"R|W|AS4"、0); // McASP 0 FIFO 控制

GEL_MapAddStr (0x01D02000、0、0x00001000、"R|W|AS4"、0); // McASP 0数据

GEL_MapAddStr (0x01D0C000、0、0x00001000、"R|W|AS4"、0); // UART 1.

GEL_MapAddStr (0x01D0D000、0、0x00001000、"R|W|AS4"、0); // UART 2.

GEL_MapAddStr (0x01D0E000、0、0x00001000、"R|W|AS4"、0); // IOPU 4.

GEL_MapAddStr (0x01D10000、0、0x00000800、"R|W|AS4"、0); // McBSP 0控制

GEL_MapAddStr (0x01D10800、0、0x00000200、"R|W|AS4"、0); // McBSP 0 FIFO 控制

GEL_MapAddStr (0x01D11000、0、0x00000800、"R|W|AS4"、0); // McBSP 1控制

GEL_MapAddStr (0x01D11800、0、0x00000200、"R|W|AS4"、0); // McBSP 1 FIFO 控制

GEL_MapAddStr (0x01E00000、0、0x00010000、"R|W|AS4"、0); // USB0 (USB HS)配置

GEL_MapAddStr (0x01E10000、0、0x00001000、"R|W|AS4"、0); // UHPI 配置

GEL_MapAddStr (0x01E11000、0、0x00001000、"R|W|AS4"、0); // UHPI (IODFT)

GEL_MapAddStr (0x01E13000、0、0x00001000、"R|W|AS4"、0); // LCD 控制器

GEL_MapAddStr (0x01E14000、0、0x00001000、"R|W|AS4"、0); // MPU 1.

GEL_MapAddStr (0x01E15000、0、0x00001000、"R|W|AS4"、0); // MPU 2.

GEL_MapAddStr (0x01E16000、0、0x00001000、"R|W|AS4"、0); // UPP

GEL_MapAddStr (0x01E17000、0、0x00001000、"R|W|AS4"、0); // VPIF

GEL_MapAddStr (0x01E18000、0、0x00002000、"R|W|AS4"、0); // SATA

GEL_MapAddStr (0x01E1A000、0、0x00001000、"R|W|AS4"、0); // PLL 控制器1

GEL_MapAddStr (0x01E1B000、0、0x00001000、"R|W|AS4"、0); // MMC/SD 1.

GEL_MapAddStr (0x01E20000、0、0x00002000、"R|W|AS4"、0); // EMAC CPPI

GEL_MapAddStr (0x01E22000、0、0x00001000、"R|W|AS4"、0); // EMAC 控制寄存器

GEL_MapAddStr (0x01E23000、0、0x00001000、"R|W|AS4"、0); // EMAC 寄存器

GEL_MapAddStr (0x01E24000、0、0x00001000、"R|W|AS4"、0); // EMAC MDIO 端口

GEL_MapAddStr (0x01E25000、0、0x00001000、"R|W|AS4"、0); // USB1 (USB FS)

GEL_MapAddStr (0x01E26000、0、0x00001000、"R|W|AS4"、0); // GPIO

GEL_MapAddStr (0x01E27000、0、0x00001000、"R|W|AS4"、0); // PSC 1.

GEL_MapAddStr (0x01E28000、0、0x00001000、"R|W|AS4"、0); // I2C 1.

GEL_MapAddStr (0x01E29000、0、0x00001000、"R|W|AS4"、0); // IOPU 3.

GEL_MapAddStr (0x01E2A000、0、0x00001000、"R|W|AS4"、0); // PBIST 控制器

GEL_MapAddStr (0x01E2B000、0、0x00001000、"R|W|AS4"、0); // PBIST 组合器

GEL_MapAddStr (0x01E2C000、0、0x00001000、"R|W|AS4"、0); //系统配置

GEL_MapAddStr (0x01E30000、0、0x00008000、"R|W|AS4"、0); // TPCC1

GEL_MapAddStr (0x01E38000、0、0x00000400、"R|W|AS4"、0); // TPTC2

GEL_MapAddStr (0x01F00000、0、0x00001000、"R|W|AS4"、0); // ePWM 0

GEL_MapAddStr (0x01F01000、0、0x00001000、"R|W|AS4"、0); // HRPWM 0

GEL_MapAddStr (0x01F02000、0、0x00001000、"R|W|AS4"、0); // ePWM 1.

GEL_MapAddStr (0x01F03000、0、0x00001000、"R|W|AS4"、0); // HRPWM 1.

GEL_MapAddStr (0x01F06000、0、0x00001000、"R|W|AS4"、0); // ECAP 0

GEL_MapAddStr (0x01F07000、0、0x00001000、"R|W|AS4"、0); // ECAP 1.

GEL_MapAddStr (0x01F08000、0、0x00001000、"R|W|AS4"、0); // ECAP 2.

GEL_MapAddStr (0x01F0B000、0、0x00001000、"R|W|AS4"、0); // IOPU 5.

GEL_MapAddStr (0x01F0C000、0、0x00001000、"R|W|AS4"、0); // Timer64P 2.

GEL_MapAddStr (0x01F0D000、0、0x00001000、"R|W|AS4"、0); // Timer64P 3.

GEL_MapAddStr (0x01F0E000、0、0x00001000、"R|W|AS4"、0); // SPI1

GEL_MapAddStr (0x01F10000、0、0x00001000、"R|W|AS4"、0); // McBSP 0 FIFO 数据

GEL_MapAddStr (0x01F11000、0、0x00001000、"R|W|AS4"、0); // McBSP 1 FIFO 数据

GEL_TextOut ("\t 内存映射设置完成。\n"、"输出"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

Set_Core_456MHz (){

DEVICE_PLL0 (0、18、0、0、1、11、5);

GEL_TextOut ("\tPLL0 init done for Core:456MHz、EMIFA:38MHz\n"、"输出"、1、1、1);

}

Set_Core_300MHz (){

DEVICE_PLL0 (0、24、1、0、1、11、5);

GEL_TextOut ("\tPLL0 init done for Core:300MHz、EMIFA:25MHz\n"、"输出"、1、1、1);

}

Set_Core_200MHz (){

DEVICE_PLL0 (0、24、2、0、1、7、3);

GEL_TextOut ("\tPLL0 init done for Core:200MHz、EMIFA:25MHz\n"、"输出"、1、1、1);

}

Set_Core_100MHz (){

DEVICE_PLL0 (0、24、5、0、1、3、1);

GEL_TextOut ("\tPLL0 init done for Core:100MHz、EMIFA:25MHz\n"、"输出"、1、1、1);

}

SET_DDRPLL_150MHz (){

DEVICE_PLL1 (24、1、0、1、2);

GEL_TextOut ("\tPLL1 init done for DDR:150MHz\n"、"输出"、1、1、1);

}

SET_DDRPLL_132MHz (){

DEVICE_PLL1 (21、1、0、1、2);

GEL_TextOut ("\tPLL1 init done for DDR:132MHz\n"、"输出"、1、1、1);

}

SET_DDRPLL_126MHz (){

DEVICE_PLL1 (20、1、0、1、2);

GEL_TextOut ("\tPLL1 init done for DDR:126MHz\n"、"输出"、1、1、1);

}

SET_DDRPLL_102MHz (){

DEVICE_PLL1 (16、1、0、1、2);

GEL_TextOut ("\tPLL1 init done for DDR:102MHz\n"、"输出"、1、1、1);

}

SET_DDR2_150MHz (){

GEL_TextOut ("\TDDR 初始化正在进行...\n"、"输出"、1、1);

SET_DDRPLL_150MHz ();

DEVICE_DDRConfig (DDR2、150);

GEL_TextOut ("\tDDR2 init for 150 MHz 已完成\n"、"输出"、1、1、1);

}

SET_DDR2_132MHz (){

GEL_TextOut ("\TDDR 初始化正在进行...\n"、"输出"、1、1);

SET_DDRPLL_132MHz ();

DEVICE_DDRConfig (DDR2、132);

GEL_TextOut ("\t132 MHz 的 DDR2初始化已完成\n"、"输出"、1、1、1);

}

SET_DDR2_126MHz (){

GEL_TextOut ("\TDDR 初始化正在进行...\n"、"输出"、1、1);

SET_DDRPLL_126MHz ();

DEVICE_DDRConfig (DDR2、126);

GEL_TextOut ("\t126 MHz 的 DDR2初始化已完成\n"、"输出"、1、1、1);

}

SET_DDR2_102MHz (){

GEL_TextOut ("\TDDR 初始化正在进行...\n"、"输出"、1、1);

SET_DDRPLL_102MHz ();

DEVICE_DDRConfig (DDR2、102);

GEL_TextOut ("\TDDR 初始化102MHz 已完成\n"、"输出"、1、1、1);

}

菜单项"频率设置"

热菜单 Core_456MHz_mDDR_150MHz (){

Set_Core_456MHz ();

SET_DDR2_150MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_300MHz_mDDR_150MHz (){

Set_Core_300MHz ();

SET_DDR2_150MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_300MHz_mDDR_132MHz (){

Set_Core_300MHz ();

SET_DDR2_132MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_300MHz_mDDR_126MHz (){

Set_Core_300MHz ();

SET_DDR2_126MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_300MHz_mDDR_102MHz (){

Set_Core_300MHz ();

SET_DDR2_102MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_200MHz_mDDR_126MHz (){

Set_Core_200MHz ();

SET_DDR2_126MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 Core_100MHz_mDDR_102MHz (){

Set_Core_100MHz ();

SET_DDR2_102MHz ();

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

菜单项"实验板"

菜单项"完整 EVM"

hotmenu PSC_all_on (){

// PSC0

PSC0_LPSC 使能(0、LPSC EDMA_cC0);

PSC0_LPSC 使能(0、LPSC EDMA_TC0);

PSC0_LPSC_ENABLE (0、LPSC_EDMA_TC1);

PSC0_LPSC_ENABLE (0、LPSC_EMIFA);

PSC0_LPSC 使能(0、LPSC SPI0);

PSC0_LPSC 使能(0、LPSC MMCSD0);

PSC0_LPSC 使能(0、LPSC ARM_AINTC);

PSC0_LPSC 使能(0、LPSC ARM_RAMROM);

PSC0_LPSC 使能(0、LPSC UART0);

PSC0_LPSC 使能(0、LPSC SCR0);

PSC0_LPSC_ENABLE (0、LPSC_SCR1);

PSC0_LPSC_ENABLE (0、LPSC_SCR2);

// PSC1

PSC1_LPSC_ENABLE (0、LPSC_EDMA_CC1);

PSC1_LPSC_ENABLE (0、LPSC_USB20);

PSC1_LPSC_ENABLE (0、LPSC_USB11);

CFGCHIP2 = 0x09F2;//启用 USB 时钟、PHY_PLLON、胶合逻辑多路复用器(USB2参考时钟输入)

PSC1_LPSC_ENABLE (0、LPSC_GPIO);

PSC1_LPSC_ENABLE (0、LPSC_UHPI);

PSC1_LPSC_ENABLE (0、LPSC_EMAC);

PSC1_LPSC_ENABLE (0、LPSC_McASP0);

PSC1_LPSC_FORCE (LPSC_SATA);

PSC1_LPSC_ENABLE (0、LPSC_SATA);

PSC1_LPSC_ENABLE (0、LPSC_VPIF);

PSC1_LPSC_ENABLE (0、LPSC_SPI1);

PSC1_LPSC_ENABLE (0、LPSC_I2C1);

PSC1_LPSC_ENABLE (0、LPSC_UART1);

PSC1_LPSC_ENABLE (0、LPSC_UART2);

PSC1_LPSC_ENABLE (0、LPSC_MCBSP0);

PSC1_LPSC_ENABLE (0、LPSC_MCBSP1);

PSC1_LPSC_ENABLE (0、LPSC_LCDC);

PSC1_LPSC_ENABLE (0、LPSC_ePWM);

PSC1_LPSC_ENABLE (0、LPSC_MMCSD1);

PSC1_LPSC_ENABLE (0、LPSC_UPP);

PSC1_LPSC_ENABLE (0、LPSC_ECAP);

PSC1_LPSC_ENABLE (0、LPSC_EDMA_TC2);

PSC1_LPSC 使能(0、LPSC SCR_F0);

PSC1_LPSC_ENABLE (0、LPSC_SCR_F1);

PSC1_LPSC_ENABLE (0、LPSC_SCR_F2);

PSC1_LPSC_ENABLE (0、LPSC_SCR_F6);

PSC1_LPSC_ENABLE (0、LPSC_SCR_F7);

PSC1_LPSC_ENABLE (0、LPSC_SCR_F8);

PSC1_LPSC 使能(0、LPSC BR_F7);

PSC1_LPSC_ENABLE (0、LPSC_SHARD_RAM);

GEL_TextOut ("\tPSC Enable Complete"、"Output"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

热菜单 EMIFA_NAND_PINMUX (){

PSC0_LPSC_ENABLE (0、LPSC_EMIFA);

PINMUX7 =(PINMUX7 &~0x00FF0FF0)| 0x00110110;

PINMUX8 = 0x11111111;

PINMUX9 = 0x11111111;

PINMUX12 =(PINMUX12 &~0x0FF00000)| 0x01100000;

EMIFA_ACFG3 |= 0x1;

EMIFA_NANDFCR =(EMIFA_NANDFCR &~0x30)| 0x12;

GEL_TextOut (为 NAND 配置的"\tEMIFA 引脚。\n"、"输出"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

/

DEVICE_PLL0初始化:

CLKMODE - 0-->片上振荡器1--->外部振荡器

PLL0_SYSCLK1 -固定比率/1

PLL0_SYSCLK2 -固定比率/2

PLL0_SYSCLK3 -可变分频器(EMIFA)

PLL0_SYSCLK4 -固定比率/4

PLL0_SYSCLK5 -未使用--不执行任何操作

PLL0_SYSCLK6 -固定比率/1

PLL0_SYSCLK7 -可变分频器(RMII)

0、24、1、1、11、5

(二 /

DEVICE_PLL0 (unsigned int CLKMODE、unsigned int PLLM、unsigned int POSTDIV、unsigned int PLLDIV1、unsigned int PLLDIV2、unsigned int PLLDIV3、unsigned int PLLDIV7){

unsigned int i=0;

/*清除 PLL 锁定位*/

CFGCHIP0 &=~(0x00000010);

/*设置 PLLENSRC '0'、位5、PLL 使能(PLLEN)选择通过 MMR 控制*/

PLL0_PLLCTL &=~(0x00000020);

对于 Freon、/* PLLCTL.EXTCLKSRC 位9应该保持为0。*/

PLL0_PLLCTL &=~(0x00000200);

/*将 PLLEN=0设置为进入旁路模式*/

PLL0_PLLCTL &=~(0x00000001);

/*等待4个周期以使 PLLEN 多路复用器正确绕过时钟*/

for (i=0;<PLLEN_MUX_SWITCH; i++) {;}

/*选择时钟模式位8作为外部时钟或片上振荡器*/

PLL0_PLLCTL &= 0xFFFFFFF;

PLL0_PLLCTL |=(CLKMODE << 8);

/*清除 PLLRST 位以复位 PLL */

PLL0_PLLCTL &=~(0x00000008);

/*禁用 PLL 输出*/

PLL0_PLLCTL |=(0x00000010);

/* PLL 初始化序列

通过将 PWRDN 位置为0 */为 PLL 加电

PLL0_PLLCTL &=~(0x00000002);

/*启用 PLL 输出*/

PLL0_PLLCTL &=~(0x00000010);

/*PLL 稳定时间-执行此步骤,当 PLL 处于旁路模式时,此处不需要此步骤*/

for (i=0;<PLL_STABILIZATION_TIME; i++) {;}

/*在 PLLM*/中编程所需的乘法器值

PLL0_PLLM = PLLM;

/*如果需要缩放给定 PLLC 的所有 SYSCLK 频率,请对 POSTDIV 比率进行编程*/

PLL0_POSTDIV = 0x8000 | POSTDIV;

/*检查 PLLSTAT 中的 GOSTAT 位是否清零以指示当前没有执行任何 GO 操作*/

while (PLL0_PLLSTAT & 0x1==1){}

/*使用所需的分频系数对 PLLDIVx 中的比率字段进行编程。 此外,确保在此步骤中保持 PLLDIVx.DxEN 位的设置,以便时钟仍然被启用(缺省值)。*/

PLL0_PLLDIV1 = 0x8000 | PLLDIV1;//固定比率/1

PLL0_PLLDIV2 = 0x8000 | PLLDIV2;//固定比率/2

PLL0_PLLDIV4=0x8000 |(((PLLDIV1+1)*4)-1);//固定比率/4

PLL0_PLLDIV6 = 0x8000 | PLLDIV1;//固定比率/1

PLL0_PLLDIV3 = 0x8000 | PLLDIV3;//可变比(EMIF)

PLL0_PLLDIV7 = 0x8000 | PLLDIV7;//可变比率(RMII)

/*将 PLLCMD 中的 GOSET 位设置为1以启动新的分频器转换。*/

PLL0_PLLCMD |= 0x1;

/*等待 PLLSTAT 中的 GSTAT 位清零(相位对齐完成)。*/

while (PLL0_PLLSTAT & 0x1==1){}

/*等待 PLL 正确复位。*/

for (i=0;<PLL_RESET_TIME_CNT; i++) {;}

/*将 PLLCTL 中的 PLLRST 位设置为1可使 PLL 退出复位*/

PLL0_PLLCTL |= 0x8;

/*等待 PLL 锁定。*/

for (i=0;<PLL_LOCK_TIME_CNT; i++) {;}

/*将 PLLCTL 中的 PLLEN 位置为1可将 PLL 从旁路模式中移除*/

PLL0_PLLCTL |= 0x1;

}

/

DDR PLL1初始化:

(三 /

DEVICE_PLL1 (unsigned int PLLM、unsigned int POSTDIV、unsigned int PLLDIV1、unsigned int PLLDIV2、unsigned int PLLDIV3){

unsigned int i=0;

/*清除 PLL 锁定位*/

CFGCHIP3 &=~(0x00000020);

/*设置 PLLENSRC '0'、位5、PLL 使能(PLLEN)选择通过 MMR 控制*/

PLL1_PLLCTL &=~(0x00000020);

对于 Freon、/* PLLCTL.EXTCLKSRC 位9应该保持为0。*/

PLL1_PLLCTL &=~(0x00000200);

/*将 PLLEN=0设置为进入旁路模式*/

PLL1_PLLCTL &=~(0x00000001);

/*等待4个周期以使 PLLEN 多路复用器正确绕过时钟*/

for (i=0;<PLLEN_MUX_SWITCH; i++) {;}

/*清除 PLLRST 位以复位 PLL */

PLL1_PLLCTL &=~(0x00000008);

/*禁用 PLL 输出*/

PLL1_PLLCTL |=(0x00000010);

/* PLL 初始化序列

通过将 PWRDN 位置为0 */为 PLL 加电

PLL1_PLLCTL &=~(0x00000002);

/*启用 PLL 输出*/

PLL1_PLLCTL &=~(0x00000010);

/*PLL 稳定时间-执行此步骤,当 PLL 处于旁路模式时,此处不需要此步骤*/

for (i=0;<PLL_STABILIZATION_TIME; i++) {;}

/*在 PLLM*/中编程所需的乘法器值

PLL1_PLLM = PLLM;

/*如果需要缩放给定 PLLC 的所有 SYSCLK 频率,请对 POSTDIV 比率进行编程*/

PLL1_POSTDIV = 0x8000 | POSTDIV;

/*检查 PLLSTAT 中的 GOSTAT 位是否清零以指示当前没有执行任何 GO 操作*/

while (PLL1_PLLSTAT & 0x1=1){}

/*使用所需的分频系数对 PLLDIVx 中的比率字段进行编程。 此外,确保在此步骤中保持 PLLDIVx.DxEN 位的设置,以便时钟仍然被启用(缺省值)。*/

PLL1_PLLDIV1 = 0x8000 | PLLDIV1;// DDR 频率(也称为2X_CLK)

PLL1_PLLDIV2 = 0x8000 | PLLDIV2;//可选的 CFGCHIP3[ASYNC3_CLKSRC]时钟源

PLL1_PLLDIV3 = 0x8000 | PLLDIV3;//可选 PLL0时钟源

/*将 PLLCMD 中的 GOSET 位设置为1以启动新的分频器转换。*/

PLL1_PLLCMD |= 0x1;

/*等待 PLLSTAT 中的 GSTAT 位清零(相位对齐完成)。*/

while (PLL1_PLLSTAT & 0x1==1){}

/*等待 PLL 正确复位*/

for (i=0;<PLL_RESET_TIME_CNT; i++) {;}

/*将 PLLCTL 中的 PLLRST 位设置为1可使 PLL 退出复位*/

PLL1_PLLCTL |= 0x8;

/*等待 PLL 锁定。 请参阅 PLL 技术规格以了解 PLL 锁定时间*/

for (i=0;<PLL_LOCK_TIME_CNT; i++) {;}

/*将 PLLCTL 中的 PLLEN 位置为1可将 PLL 从旁路模式中移除*/

PLL1_PLLCTL |= 0x1;

}

/

设备脚踢解锁:

Kick0寄存器+数据(解锁)

Kick1寄存器+数据(解锁)

(三 /

device_fickUnlock(){

KICK0R = 0x83e70b13;// Kick0寄存器+数据(解锁)

KICK1R = 0x95a4f1e0;// Kick1寄存器+数据(解锁)

GEL_TextOut ("\tKICK 未锁定。\n"、"输出"、1、1);

GEL_TextOut ("\t\t----------------- \n"、"输出"、1、1、1);

}

/

PSC 常用功能:

(三 /

/*不带握手的力模块状态*/

PSC1_LPSC_FORCE (无符号 int LPSC_num){

*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)| 0x8000000);

}

/*SyncReset 函数,用于 PSC1*/

PSC1_LPSC_SyncReset (unsigned int pd、unsigned int LPSC_num){

unsigned int j;

if ((*(unsigned int*)(PSC1_mdstat+4 * LPSC _num)& 0x1F)!= 0x1){

*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)& 0xFFFFFFE0)| 0x0001;

PSC1_PTCMD = 0x1<<PD;

J = 0;

/*等待电源状态转换完成*/

while (((PSC1_PTSTAT 和)(0x1<PSC1_<PD) ) !=0) {

if (j++> psc_timeout){

GEL_TextOut ("\tPSC1同步重置转换超时、域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC _num);

中断;

}

}

J = 0;

while ((*(unsigned int*)(PSC1_mdstat+4 * LPSC _num)& 0x1F)!=0x1){

if (j++> psc_timeout){

GEL_TextOut ("\tPSC1同步重置验证域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上的超时);

中断;

}

}

}

}

/*启用 PSC1*/的功能

PSC1_LPSC_ENABLE (unsigned int pd、unsigned int LPSC_num){

unsigned int j;

if ((*(unsigned int*)(PSC1_mdstat+4 * LPSC _num)& 0x1F)!= 0x3){

*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC1_MDCTL+4*LPSC_num)& 0xFFFFFFE0)| 0x0003;

PSC1_PTCMD = 0x1<<PD;

J = 0;

/*等待电源状态转换完成*/

while (((PSC1_PTSTAT 和)(0x1<PSC1_<PD) ) !=0) {

if (j++> psc_timeout){

GEL_TextOut ("\tPSC1在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上启用转换超时);

中断;

}

}

J = 0;

while ((*(unsigned int*)(PSC1_mdstat+4 * LPSC _num)& 0x1F)!=0x3){

if (j++> psc_timeout){

GEL_TextOut ("\tPSC1在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上启用验证超时);

中断;

}

}

}

}

/*LPSC ARM 或 DSP*/的启用功能

PSC0_LPSC enableCore (unsigned int pd、unsigned int LPSC num){

unsigned int j;

if ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x11F)!= 0x103){

*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)& 0xFFFFFE0)| 0x0103;

PSC0_PTCMD = 0x1<<PD;

J = 0;

/*等待电源状态转换完成*/

while (((PSC0_PTSTAT &)(0x1<PSC0 <PD) ) !=0) {

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC _num 上启用内核转换超时);

中断;

}

}

J = 0;

while ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x11F)!=0x103){

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC _num 上启用内核验证超时);

中断;

}

}

}

}

/*SyncReset 函数,用于 PSC0*/

PSC0_LPSC_SyncReset (unsigned int pd、unsigned int LPSC_num){

unsigned int j;

if ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x1F)!= 0x1){

*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)& 0xFFFFFFE0)| 0x0001;

PSC0_PTCMD = 0x1<<PD;

J = 0;

/*等待电源状态转换完成*/

while (((PSC0_PTSTAT &)(0x1<PSC0 <PD) ) !=0) {

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC _num 上的同步复位转换超时);

中断;

}

}

J = 0;

while ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x1F)!=0x1){

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0同步重置验证域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上的超时);

中断;

}

}

}

}

/*启用 PSC0*/的功能

PSC0_LPSC 使能(unsigned int pd、unsigned int lpsc_num){

unsigned int j;

if ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x1F)!= 0x3){

*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)=(*(unsigned int*)(PSC0_MDCTL+4*LPSC_num)& 0xFFFFFFE0)| 0x0003;

PSC0_PTCMD = 0x1<<PD;

J = 0;

/*等待电源状态转换完成*/

while (((PSC0_PTSTAT &)(0x1<PSC0 <PD) ) !=0) {

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上启用转换超时);

中断;

}

}

J = 0;

while ((*(unsigned int*)(PSC0_mdstat+4 * LPSC _num)& 0x1F)!=0x3){

if (j++> psc_timeout){

GEL_TextOut ("\tPSC0在域%d、LPSC %d\n"、"输出"、1、1、1、PD、LPSC num 上启用验证超时);

中断;

}

}

}

}

/

DDR 配置例程:

1. DDR 使能

2. VTP 校准

3.配置 DDR

4.设置为自刷新、启用 mclkstop 和 DDR 同步复位

5.启用 DDR 和禁用自刷新

内部频率为 MHz

DDR2 = 0

mDDR = 1.

DDR 配置电子表格工具位于此处:

processors.wiki.ti.com/.../C674x

(三 /

DEVICE_DDRConfig (unsigned int DDR_type、unsigned int freq)

{

unsigned int j;

unsigned int tmp_sdcr;

//启用 EMIFDDR SDRAM 的时钟

PSC1_LPSC_ENABLE (PD0、LPSC_DDR);

//开始 VTP 校准

VTPIO_CTL &=~0x00000040;//清除 POWERDN

VTPIO_CTL &=~0x00000080;//清除锁定

VTPIO_CTL |= 0x00002000;//设置 CLKRZ 以防它之前被清除(VTP 查找 CLKRZ 边沿转换)

VTPIO_CTL &&~0x00002000;//清除 CLKRZ (使用读-修改-写来确保1个 VTP 周期等待前一条指令)

VTPIO_CTL |= 0x00002000;//设置 CLKRZ (使用读-修改-写来确保1个 VTP 周期等待前一条指令)

J = 0;

//轮询就绪位以查看 VTP 校准何时完成

while (((VTPIO_CTL 和0x00008000)= 0){

if (j++>vt_timeout){

GEL_TextOut ("\tVTP 就绪超时\n"、"输出"、1、1);

中断;

}

}

VTPIO_CTL |= 0x00000080;//为静态校准模式设置 LOCK 位

VTPIO_CTL |= 0x00000040;//设置 POWERDN 位以关闭 VTP 模块

//结束 VTP 校准

VTPIO_CTL |= 0x00004000;//设置 IOPWRDN 以在 PWRDNEN 置1时允许输入接收器断电

//

//设置1Gb DDR2 Samsung K4T1G164QF-BCF8

//配置 DDR 时序

DRPYC1R =(0x0 << 8)|//保留

(0x1 << 7)|// EXT_STRBEN

(0x1 << 6)|// PWRDNEN

(0x0 << 3)|//保留

(0x4 << 0);// RL

// DRPYC1R 值= 0x000000C4

if (DDR_DEBUG){

//使用最大时序配置 EMIF 以实现更长的可宽延时间

//如果内存不稳定,请尝试此操作

DRPYC1R |= 0x7;// RL

}

EMIFDDR_SDCR |= 0x00800000;//设置 BOOTUNLOCK

//设置取决于 DDR2

TMP_SDCR =(0x0 << 25)|// MSDRAMEN

(0x1 << 20);// DDR2EN

GEL_TextOut ("\t 使用 DDR2设置\n"、"输出"、1、1);

EMIFDDR_SDCR = tmp_SDCR |//设置根据 DDR2或 mDDR 而变化

(EMIFDDR_SDCR 和0xF0000000)|//保留

(0x0 << 27)|// DDR2TERM1

(0x0 << 26)|// IBANK_POS

(0x0 << 24)|// DDRDRIVE1

(0x0 << 23)|// BOOTUNLOCK

(0x0 << 22)|// DDR2DDQS

(0x0 << 21)|// DDR2TERM0

(0x0 << 19)|// DDRDLL_DIS

(0x0 << 18)|// DDRDRIVE0

(0x1 << 17)|// DDREN

(0x1 << 16)|// SDRAMEN

(0x1 << 15)|// TIMUNLOCK

(0x1 << 14)|// nm

(0x0 << 12)|//保留

(0x4 << 9)|// CL

(0x0 << 7)|//保留

(0x3 << 4)|// IBANK

(0x0 << 3)|//保留

(0x2 <<0);//页大小

EMIFDDR_SDCR2 = 0x00000000;// IBANK_POS 设置为0、因此该寄存器不适用

if (DDR_DEBUG){

//使用最大时序配置 EMIF 以实现更长的可宽延时间

//如果内存不稳定,请尝试此操作

EMIFDDR_SDTIMR1 =(0x7F << 25)|// tRFC

(0x07 << 22)|// TRP

(0x07 << 19)|// tRCD

(0x07 << 16)|// TWR

(0x1f << 11)|// tras

(0x1f << 6)|// TRC

(0x07 <<3)|// tRRD

(EMIFDDR_SDTIMR1和0x4)|//保留

(0x03 <<0);// tWTR

EMIFDDR_SDTIMR2 =(EMIFDDR_SDTIMR2和0x8000000)|//保留

(((unsigned int)((70000 / 3400)- 0.5))<< 27)|// tRASMAX (原始7812.5)

(0x3 << 25)|// TxP

(0x0 << 23)|// tODT (不支持)

(0x7f << 16)|// tXSNR

(0xFF << 8)|// tXSRD

(0x07 <<5)|// tRTP (1周期)

(0x1f << 0);// tCKE

GEL_TextOut ("\TDDR 时序配置用于调试\n"、"输出"、1、1、1);

}

否则{

//让 float ->整数截断句柄减1;更安全地针对计时进行舍入

EMIFDDR_SDTIMR1 =((unsigned int)(127.5 * freq / 1000))<< 25)|// tRFC

(((unsigned int)(13.13 * freq / 1000))<< 22)|// TRP

(((unsigned int)(13.13 * freq / 1000))<< 19)|// tRCD

(((unsigned int)(15.0 * freq / 1000))<< 16)|// TWR

(((unsigned int)(45.0 * freq / 1000))<< 11)|// tras

(((unsigned int)(58.13 * freq / 1000))<< 6)|// trc

(((unsigned int)(7.5 * freq / 1000))<< 3)|// tRRD

(EMIFDDR_SDTIMR1和0x4)|//保留

(((2 - 1)<< 0);// tWTR

EMIFDDR_SDTIMR2 =(EMIFDDR_SDTIMR2和0x8000000)|//保留

(((unsigned int)((70000 / 7800)- 1))<< 27)|// tRASMAX (原始3400)

((0x3-1)<< 25)|// TxP (应为6-1、符合 MT46H64M16LFBF-6数据表、但字段最多为0b11)

(0x0 << 23)|// tODT (不支持)

(((unsigned int)(137.5 * freq / 1000))<< 16)|// tXSNR (对于 mDDR 为 tXSR)

((200-1)<< 8)|// tXSRD (对于 mDDR 为 tXSR)

((2 - 1)<< 5)|// tRTP

(((3 - 1)<< 0);// tCKE

}

EMIFDDR_SDCR &=~0x00008000;//清除 TIMUNLOCK

//让浮点->整数截断句柄 RR 舍入;刷新率更安全地舍入

EMIFDDR_SDRCR =(0x1 << 31)|// LPMODEN (LPSC SyncReset/Enable 需要)

(0x1 << 30)|// MCLKSTOPEN (LPSC SyncReset/Enable 需要)

(0x0 << 24)|//保留

(0x0 << 23)|// SR_PD

(0x0 << 16)|//保留

(((unsigned int)(7.8 * freq))<< 0);// rr (原始版本7.8125)

//同步将时钟重置为 EMIFDDR SDRAM

PSC1_LPSC_SyncReset (PD0、LPSC_DDR);

//启用 EMIFDDR SDRAM 的时钟

PSC1_LPSC_ENABLE (PD0、LPSC_DDR);

//禁用自刷新

EMIFDDR_SDRCR &=~0xC0000000;

EMIFDDR_PBBPR = 0x30;

}

但是、通过串行端口不显示 DDR2设置中的任何内容、

在内部 DSPL2RAM 中、SIR 工作正常。

我要添加的任何特定入口点、因为它禁用了我使用的。

能不能给我一些建议。

谢谢您、

此致、

Ramachandra