请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320C6655 您好、专家、

我想得到有关电源提升(IO 之前的内核)的确认如下:

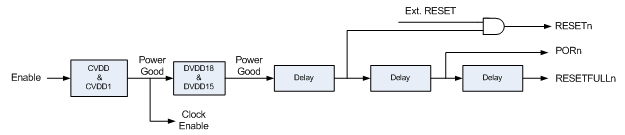

根据 EVM 设计、它使用 FPGA 通过在状态转换之间使用5ms 延迟来控制斜升序列和复位信号。 在某些 E2E 讨论中、某些设计使用8ms 或11ms 延迟。 但是、我在数据表中没有找到这方面的时序规格、除了在器件初始化阶段释放前100us + 16us 的延迟。 在每个状态转换中使用几毫秒延迟是否有任何特殊的要求?

对此,

系统