尊敬的先生/女士:

我们正在开发一个定制电路板、其中包含 DRA76P 以及 QSPI 和 eMMC 闪存器件。 QSPI P/N 为 S25FL256ASGMFV001、eMMC 为 MTFC8GAMALNA-AAT。

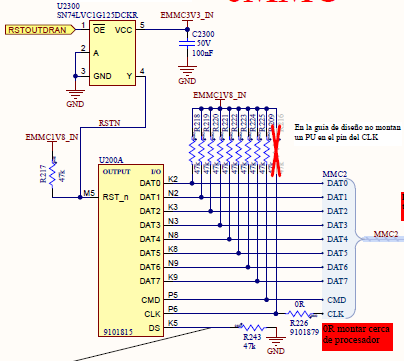

QSPI 工作正常。 而不是 eMMC 存储器。 它们的连接方式如下所示:

我们能够使用 fastboot.sh (包含在预编译中)进行刷写、而不会出现错误。

在 u-boot 中、我们将获取下一个信息:

从 mmcinfo 中:

器件:OMAP SD/MMC 制造商 ID:13 OEM:14E 名称:S0J35 Tran 速度:200000000 Rd 块 Len:512 MMC 版本4.0 高容量:是 容量:7.3 GiB 总线宽度:8位 擦除组大小:512 Kib

在 EVM MMC 版本中检测到4.5...

来自 ext2ls MMC 1:11

4096。 4096 4096基准测试 4096丢失+发现 4096个否定

我们将引导 Android。 如果我们没有错,这是数据分区内容,在第一次引导之前,系统、供应商等... 将被创建。

我们已将 env 配置为从 dev 1引导

mmcboot=if MMC dev ${mmcdev};然后 setenv devtype MMC;如果 MMC 重新扫描;然后回显在器件${mmcdev}上找到的 SD/MMC;如果运行 loadimage;然后运行 loadfdt;从 mmc${mmcdev}回显引导...;运行 args_MMC;bootz ${addr}-${faddr};mmdfi = load1;mmcdf

但没有引导...

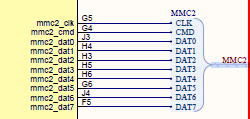

这是我们正在使用的 DTS 配置:

&mmc2{ status ="oke"; VMMC-supply =<&VIO_1v8>; 总线宽度=<8>; 最大频率=<192000000>; ti、不可拆卸; TI、双电压; CAP-MMC-highspeed; pinctrl-names ="default"、"hs"、"DDR_1_8v"、 "hs200_1_8v"; pinctrl-0 =<&mmc2_PINS_DEFAULT>; pinctrl-1 =<&mmc2_PINS_h>; pinctrl-2 =<&mmc2_PINS_DDR>; pinctrl-3 =<&mmc2_PINS_HS200 &mmc2_PIN_dre延 时 ;}

mmc2_PIN_DEFAULT:mmc2_PIN_DEFAULT{ pinctrl-single、PIN=< DRA7XX_CORE_IOPAD (0x349c、PIN_INPULL_PULLUP | MUX_MODE1)/* GPMC_A23.mmc2_CLK */ DRA7XX_CORE_INPULLUX (0x34b0_MODE2) */DRA7XX_MODE_IN_MOUX24_IN_MOUX24_IN_MOUX_IN_MODE1 */RM_INUX24_MODE_IN_IN_MOUX24_MOUX24_IN_MOUX_IN_IN_MOUX24_IN_MODE_MOUX24_IN_MODE_IN_MOUX24_IN_IN_MOUX24_IN_MOUX_IN_IN_MOUX24_MODE_IN_MOUX24_IN_IN_MODE_INPUOUX_IN_MOUX_IN_IN_MOUV/ 0x7XX_ PIN_INPULLUP | MUX_MODE1)/* GPMC_A19.mmc2_DAT4 */ DRA7XX_CORE_IOPAD (0x3490、PIN_INPUT_PULLUP | MUX_MODE1)/* GPMC_A20.mmc2_DMUX_RAPULL_OPAGEL (0x342*、 0xMC_IN_INPUT_MODE2* = 0xMC_INUX_INPLUM24_MODE2*、0xMC_INU_INPULLUM_LM_PULLUP) *| 0xMC_IN_INU_MODE2*= 0x94_MODE2_IN_MODE_IN_MODE2* 0xMC_INPULCC_MODE2*| 0xMC_MODE2_PULLUM24_IN_IN_IN_MODE_MODE_INPULLUP **、0xMC_IN_IN_IN_MODE2*= 0xMC_MODE_INPULLUP *、0xMC_IN_IN_IN_IN_IN_ PIN_INPULLUP | MUX_MODE1)/* GPMC_A24.mmc2_DAT0 */ DRA7XX_CORE_IOPAD (0x34a4、PIN_INPUT_PULLUP | MUX_MODE1)/* GPMC_A25.mmc2_DIOPT_INPUT (0x3420_MMC_MODE2 ) */0x3420_IN_MODE_IN_MOUX_INPUT (0x27_MOUX_DMUX_DAC_MODE4)*/RM42_IN_MODE_INPULLUC24_AD_MODE_AD_IN_MOUX_RAPULLUP * **/0x27_MODE_MODE_MODE_IN_MODEV (0x27_MODE_IN_MODE_IN_MODE_MODEV */0x27_IN_IN_MODE_MODE_IN_MOUX_INPUT)* 0x27_MOUX_INPUT (0x27_MODE_IN_MODE_MODE_MODEV * 0x PIN_INPULLUP | MUX_MODE1)/* GPMC_A22.mmc2_DAT7 * />; }; mmc2_PIN_DDR:mmc2_PIN_DDR{ pinctrl-single、引脚=< DRA7XX_CORE_IOPAD (0x349c、PIN_INPUT_PULLUP | MMC_IN_MOUX_1* 0xMC_MOUCC_1*/0x24_MODE_IN_MOUX_1* 0x24_MOUCC_IN_MODE_INPUMPUDIO2*/0x24_MODE_MODE_MODE_DON_MOUX_1* 0x24_MODE_MOUX_1*/DRA7XX_MODE_INPULLUPULLUPULLUPULLUP **/0x24_MODE_MODE_MODE_IN_MODE_IN_MODE_IN_MODE_AD_IN_MODE_MOUX_1* 0x27_IN_MODE_AD_AD_IN_MODE_INPUV/ 0xMC_ PIN_INPULLUP | MUX_MODE1)/* GPMC_A27.mmc2_DAT3 */ DRA7XX_CORE_IOPAD (0x348c、PIN_INPUT_PULLUP | MUX_MODE1)/* GPMC_A19.mmc2_datpullup * * DRA7XX_INCORE_IN_INPUT (0x3420_MMC_IN_INUX_INPULLUP) *= 0x29_MO2*、0xMC_IN_IN_INUX_INUCC_INPULLUM24_IN_IN_IN_MODE2*= 0x24_IN_IN_IN_IN_IN_IN_IN_INUX_INPULLUP (0x20_MODE2*、0xMC_IN_IN_IN_INUX_INUX_INPULLUPULLUP)*、0x200_MODE2*、0xMC_IN_IN_IN_IN_IN_IN_MODE2*= 0xMC_IN_IN_IN_MODE2*= 0xMC_IN_ /* GPMC_A23.mmc2_clk */ DRA7XX_CORE_IOPAD (0x34b0、PIN_INPUT_PULLUP | MODE1)/* GPMC_CS1.mmc2_cmd * DRA7XX_CORE_POLUP (0x34a0、PIN_INPUT_MODE1)* 0xMC_MODE2_MODE2_MODE_MOUX_MODE2 ***/0x24_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MOUX_1****/ 0x24_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE2 (0x24_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MOUX_1********/ 0x24_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE PIN_INPUT_PULLUP | MODE1)/* GPMC_A19.mmc2_DAT4 */ DRA7XX_CORE_IOPAD (0x3490、PIN_INPUT_PULLUP | MODE1 | MUX_MODE1)/* GPMC_A20.mmCORE_DIO5 **(0x3490、PIN_IN_PULLUM2_MOUDIO21 )| MODE2_MODE_MODIO2*| GPMC_MODIO2_MOU_MODE_MOU_MODIO2*| IN_PULLUX | IN_MODIO2_MOU_MODE_MODE_MODE_MOU_MOU_MODE41 *| GPMC_MODIO2_MOU_MODE_MODE_MODE_MODE_MODE_MODE_MODE_MODE

/*对应于 datamanual 中的 MMC2_HS200_MANUAL1 */ mmc2_iodelay_HS200_conf:mmc2_iodelay_HS200_conf{ pinctrl-single、pins =< 0x190 (A_delay (384)| G_delay (0))) /* CFG_GPMC_A19_oen */ 0x194 (A_DELAY (0)| G_DELAY (174)) /* CFG_GPMC_A19_OUT */ 0x1a8 (A_DELAY (410)| G_DELAY (0)) /* CFG_GPMC_A20_oen */ 0x1ac (A_DELAY (85)| G_DELAY (0)) /* CFG_GPMC_A20_OUT */ 0x1b4 (A_DELAY (468)| G_DELAY (0)) /* CFG_GPMC_A21_oen */ 0x1b8 (A_DELAY (139)| G_DELAY (0)) /* CFG_GPMC_A21_OUT */ 0x1c0 (A_DELAY (676)| G_DELAY (0)) /* CFG_GPMC_A22_oen */ 0x1c4 (A_DELAY (69)| G_DELAY (0)) /* CFG_GPMC_A22_OUT */ 0x1d0 (A_DELAY (1062)| G_DELAY (154))/* CFG_GPMC_A23_OUT */ 0x1d8 (A_DELAY (640)| G_DELAY (0)) /* CFG_GPMC_A24_oen */ 0x1dc (A_delay (0)| G_delay (0)) /* CFG_GPMC_A24_OUT */ 0x1e4 (A_DELAY (356)| G_DELAY (0)) /* CFG_GPMC_A25_oen */ 0x1e8 (A_DELAY (0)| G_DELAY (0)) /* CFG_GPMC_A25_OUT */ 0x1f0 (A_DELAY (579)| G_DELAY (0)) /* CFG_GPMC_A26_oen */ 0x1F4 (A_DELAY (0)| G_DELAY (0)) /* CFG_GPMC_A26_OUT */ 0x1fc (A_DELAY (435)| G_DELAY (0)) /* CFG_GPMC_A27_oen */ 0x200 (A_DELAY (36)| G_DELAY (0)) /* CFG_GPMC_A27_OUT */ 0x364 (A_DELAY (759)| G_DELAY (0)) /* CFG_GPMC_CS1_OEn */ 0x368 (A_DELAY (72)| G_DELAY (0)) /* CFG_GPMC_CS1_OUT */ >; };

是否对正在发生的情况有任何想法?

非常感谢!