请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:66AK2G12 你(们)好

是否存在可行性?

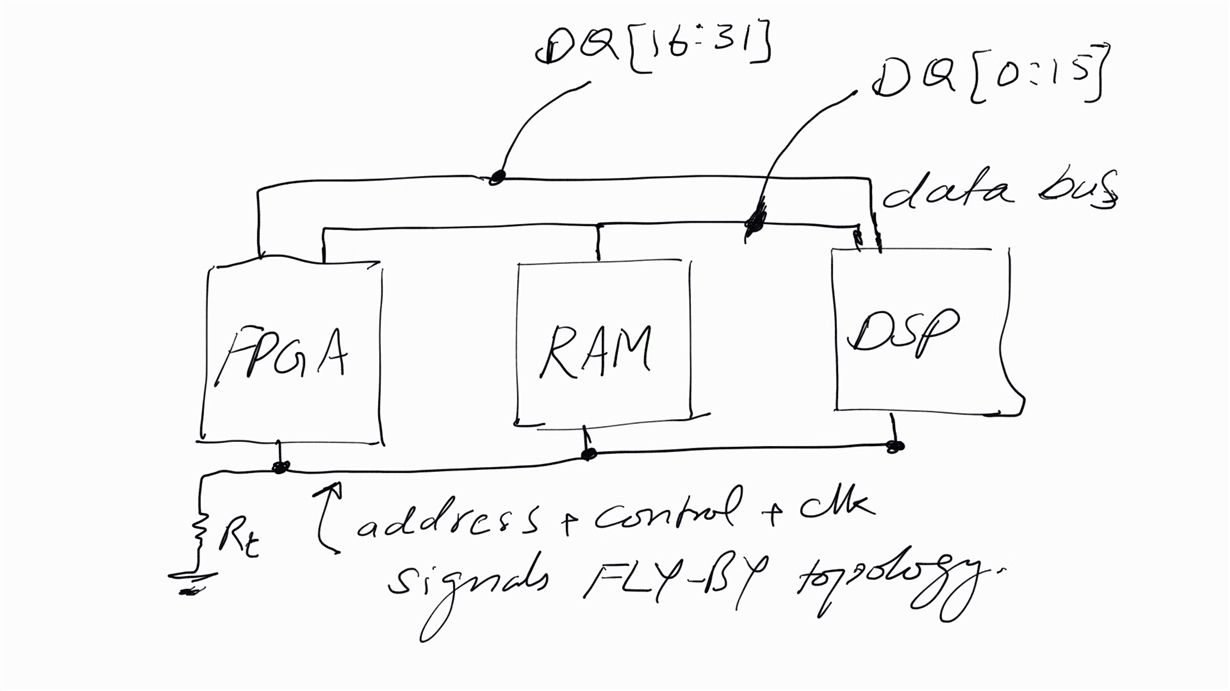

如果我使用一个 DRAM。

>第一步> FPGA 通过 DDR 接口将数据从写入 DRAM。 (16位)。

>第2步> 66AK2G12通过 DDR 接口从同一 DRAM 读取数据。 (16位)。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我不会说这是不可能的、因为我不知道这一点。 我知道的是、到 FPGA 的高速链路是 PCIe。 这样、用户仍然可以将 DDR RAM 用作 DSP 和 FPGA 之间的口袋型缓冲器。 在 DSP 端、有 DMA、即 EDMA3引擎在无需 CPU 干预的情况下执行数据移动。 特别是、可以指示它从 FPGA 中提取数据到所需位置。 请记住、这需要 FPGA 设计能够处理 PCIe 上的多双字节 TLPS、这可能会使 FPGA 设计人员付出一些努力。 另一种可能是在 FPGA 端使用 DMA 引擎以及总线主控功能。 然后、FPGA 可以自行将数据推送到 DSP 的存储器中。 我们使用后一种方法已经有一段时间了,但却放弃了前一种方法。