主题中讨论的其他器件:TMDSICE3359

您好!

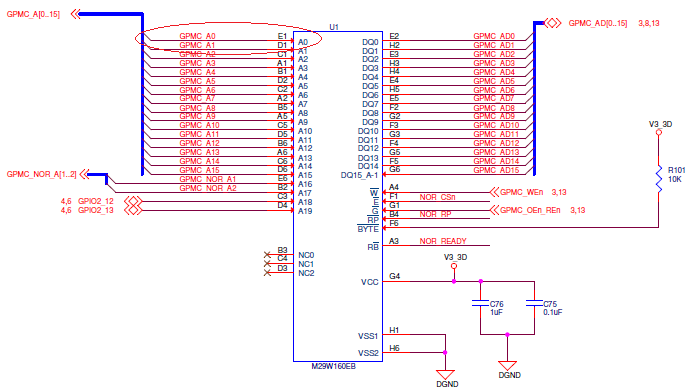

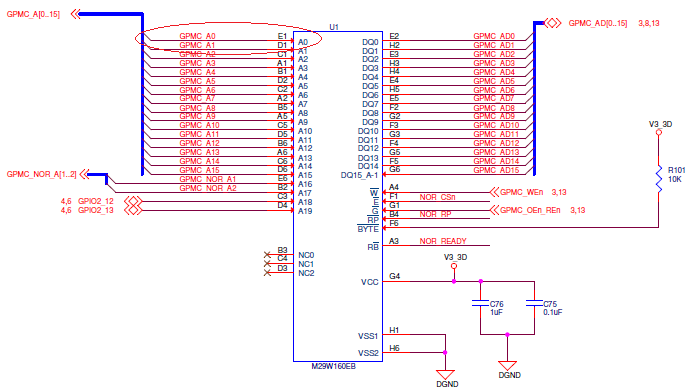

我们需要对通过 GPMC 连接16位 NOR 闪存进行澄清。

根据16位器件的 TRM "表7-5"、在这种情况下不使用 GPMC_A0

说明(TMDSICE3359) GPMC_A0似乎连接到存储器器件的 A0。

此连接是否有任何原因? 这是 EVM 设计中的一个错误。

在实际设计中、我们不需要将 GPMC_A0连接到存储器的 A0引脚、而是将 GPMC_A1连接到存储器的 A0引脚?

此致

库米

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们需要对通过 GPMC 连接16位 NOR 闪存进行澄清。

根据16位器件的 TRM "表7-5"、在这种情况下不使用 GPMC_A0

说明(TMDSICE3359) GPMC_A0似乎连接到存储器器件的 A0。

此连接是否有任何原因? 这是 EVM 设计中的一个错误。

在实际设计中、我们不需要将 GPMC_A0连接到存储器的 A0引脚、而是将 GPMC_A1连接到存储器的 A0引脚?

此致

库米

感谢 Biser、

对于高位地址线(A12-A27)、在 XIP 模式下、

TRM 提到、我们需要在 NOR 启动期间隔离高位地址行、如下所示。

"需要使用外部逻辑来隔离的上地址线(A12–A27)

NOR 从器件引脚闪存、并在非多路复用或引导期间将其驱动为低电平。"

隔离高位地址线的首选方法是什么?

由于此应用具有成本和空间限制、因此我们无法使用额外的逻辑 IC。

是否可以使用简单的电阻器下拉高位地址线?

此致

库米

您好、Biser、

谢谢你。

请允许我再澄清一个问题。

在 XIP 模式(MUX2)下、对于高地址线(A12–A27)、

我们将使用外部下拉电阻器在非多路复用或非引导期间将这些引脚驱动为低电平。

但 NOR 闪存需要地址行 A0-A24、因此我们不会使用 A25到 A27。

我们是否需要下拉地址行、即使地址行未被使用。

通过查看数据表、引脚 A25至 A27的焊球复位状态似乎很低、

因此、我们认为没有必要将 A25下拉至 A27。

请告诉我这一假设是否正确。

此致

库米