Thread 中讨论的其他器件:SYSBIOS

工具/软件:TI-RTOS

您好!

我使用定制的 K2L 板通过 EMIF-16通过 EDMA3将16位数据从 CPLD 传输到 DDR3存储器、我的问题是 EDMA 或 DMA 完成中断需要一些"唤醒"、直到它开始全速工作。

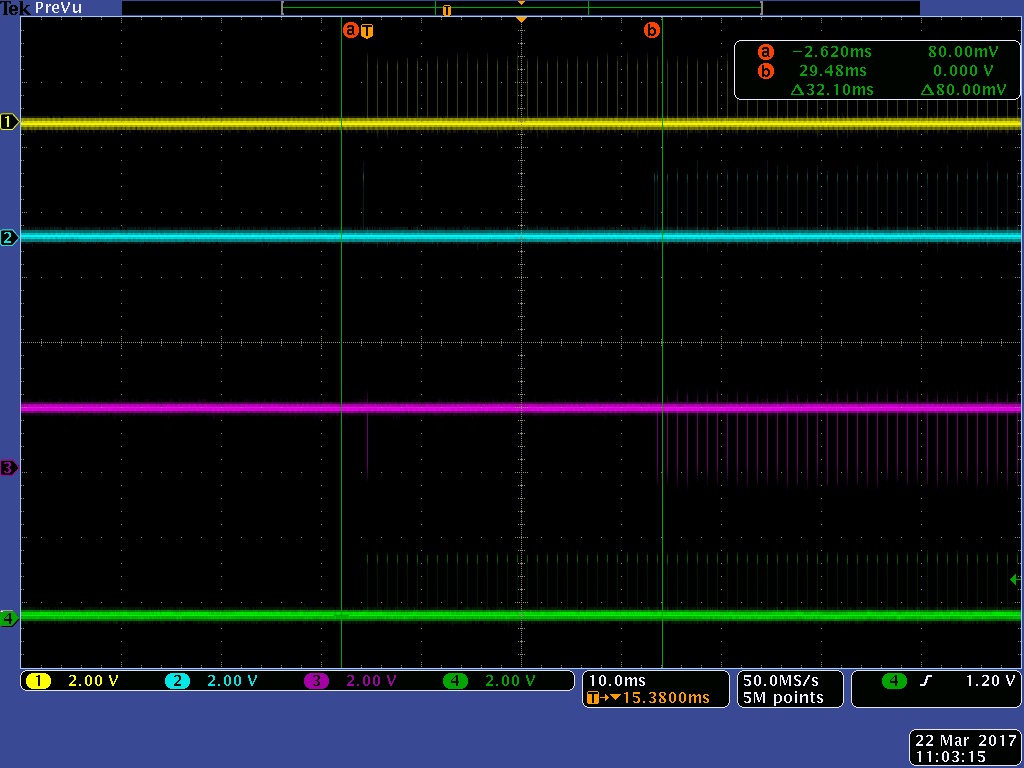

除了传输开始时 EDMA 休眠30毫秒外、一切看起来都很好。 请参阅下面的示波器图:

黄色信号显示了从 CPLD 到 C66 DSP CPU 的事件(GPIO 10)。

蓝色信号(GPIO 9)显示何时执行 DMA 完成中断。

紫色信号是 EMIF 读取信号。

绿色信号用于激活 CPLD 以执行其任务、进而导致黄色信号从 CPLD 中发出。

图中显示、当 C66 DSP CPU 启用绿色信号时、CPLD 会立即唤醒、EDMA 会从 EMIF-16读取一个信号。 然后它停止工作30毫秒。 为什么??? 唤醒后、它不再睡眠。 它可以继续工作几个小时。

在启用绿色信号之前、已配置 EDMA 及其中断、之后不再对其进行修改。 启用绿色信号后没有什么特别的发生、相同的传输应一直持续到 CPU 最终禁用绿色信号为止。

DMA 参数

OPT:0x80112004

SRC:0x34000080

AB-CNT:0x000C0002

DST:0xA0000180

BIDX: 0x00200040

链接重新加载:0xFFFFFF0000

CIDX:0x00020000

C-CNT:0x00000010

DMA 完成会触发一个中断、该中断会更新目标地址并重新启用传输。 每个事件进行12个16位数据传输、每个绿色信号脉冲重复16次。 在上面的示波器图中看不到这种情况(脉冲在屏幕上彼此太近)、但我更仔细地看了一下、就证明了这种情况是正常的。

我已经尝试调整 HWI 中断优先级和 SYS/BIOS 任务优先级、但它们没有帮助。 没有其它可取代 EDMA 完成 ISR 的有效中断。 我还尝试删除 EDMA 事件丢失中断和 CC 错误中断。 没有影响。

我尝试在不同频率下提供事件:100Hz、300Hz、1kHz、10kHz 和40kHz。 睡眠时间始终相同:30毫秒。

我在代码中设置如下任务和中断:

进行 EDMA (使用 EDMA3 LLD、TI 的驱动程序)、GPIO、CPLD 和 EDMA3中断(完成、事件丢失、cc 错误)所有设置的主任务。

STACKSIZE = 0x2000;

优先级= 0;//最初为5

运行所有非时间关键型功能的空闲循环。 目前、它是空的、什么也不做。 最初、它作为永无休止的 while 循环包含在主任务中。

idleFxns[0]="&mainTask";

EDMA 完成中断是一个自动具有最高优先级的 HWI 任务、对吧? 我像这样设置中断:

CpIntc_dispatchPlug (40、ISR_handler、0、true);

CpIntc_mapSysIntToHostInt (0、40、68);

CpIntc_enableHostInt (0、68);

EventCombiner_dispatchPlug (26、(ti_SYSBIOS_family_c64p_EventCombiner_FuncPtr) CpIntc_Dispatch、68、true);

EventCombiner_enableEvent (26);

40 = CIC0 EMDMACC_0_TC_2_INT、EDMA 事件 18 (GPIO 10)在 EDMA3 LLD 封装中包含的"ccXferCompInt"数组中分配给该事件。

26 = C66 CorePac 主中断 CIC_OUT68_PL_10_MUL_N

"ISR_handler"函数(伪语言):

ISR_handler (const EDMA3_RM_Obj * rmObj)

{

将 GPIO 9设置为"1"、这在示波器中可见(蓝色信号)

while (IPR &(1 << 18)){

ICR =(1 << 18);

}

ESR =(1 << 18);

更新 DMA 目标

为未来事件做好 EDMA 准备

将 GPIO 9设置为"0"、这在示波器中可见(蓝色信号)

}

所用工具的版本:

编译器:TI v7.4.16

CCS:v6.1.1

XDCtools:3.30.00.60

SYS/BIOS:6.45.1.29 [6.42.2.29] <-- 这是否意味着该项目最初是使用较新版本构建的,但该 PC 上只安装了6.42.2.2.29? 这是否会有这样的效果?

IPC:3.35.01.07

PDK:3.01.03.06

EDMA3 LLD:02.11.13.17

这是我所做配置中的错误、还是 SYS/BIOS 或 EDMA 控制器本身中的错误?

此致、

Ari