工具/软件:TI-RTOS

您好!

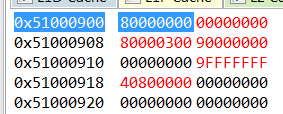

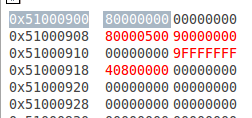

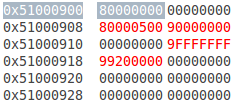

我 用 DSP1来控制 PCIe 子系统、即2xlan Gen2 RC。 EP 是 FPGA。 RC 存储器读取请求正常、如果入站存储器目标是 DSP 本地 L2-RAM、则 EP 写入请求也有效。 但是、如果我对外部 DDR 存储器执行相同的操作、则会失败。

DSP 在具有 PDK 1.0.4和 SYS/BIOS 6.46.0.23的 TI/RTOS 上运行。 它通过 Linux 中的 remoteproc (PROCESSOR-SDK-LINUXT-AM57xx-EVM-03.01.00.06)引导、并在其资源表中具有 DDR 存储器区域的所有必需插件。

MMU 失败时没有错误(PCIe 数据路径 MMU 已禁用)、请求不会被拒绝、因为不受支持-实际上一切似乎都很好、除了数据从未进入内存。

我错过了什么吗? 我是否必须为 PCIe 子系统授予 DDR 的任何访问权限? 由于 L2 RAM 地址是本地地址、我必须将其转换为全局 L3-Main 地址空间。 我不需要对 DDR-RAM 地址执行此操作、因为它已经是全局性的-我对吗?

提前感谢、

Tim