你(们)好

我们在其中一个设计中使用 X5777BXGABC 处理器。在这种情况下、我无法访问连接到 EMIF2控制器的 DDR3L 芯片(1GB)。

我尝试用减少的时钟连接 JTAG、但无法访问任何 DDR 寄存器。

我可以通过探测观察到的一件事是 EMIF2的 CKE 不会切换、 其空闲 状态为高电平(Vtt)。

是否有人可以帮助我进一步调试此问题?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

我们在其中一个设计中使用 X5777BXGABC 处理器。在这种情况下、我无法访问连接到 EMIF2控制器的 DDR3L 芯片(1GB)。

我尝试用减少的时钟连接 JTAG、但无法访问任何 DDR 寄存器。

我可以通过探测观察到的一件事是 EMIF2的 CKE 不会切换、 其空闲 状态为高电平(Vtt)。

是否有人可以帮助我进一步调试此问题?

Anand、

很抱歉耽误你的回答。 我是 ooo。

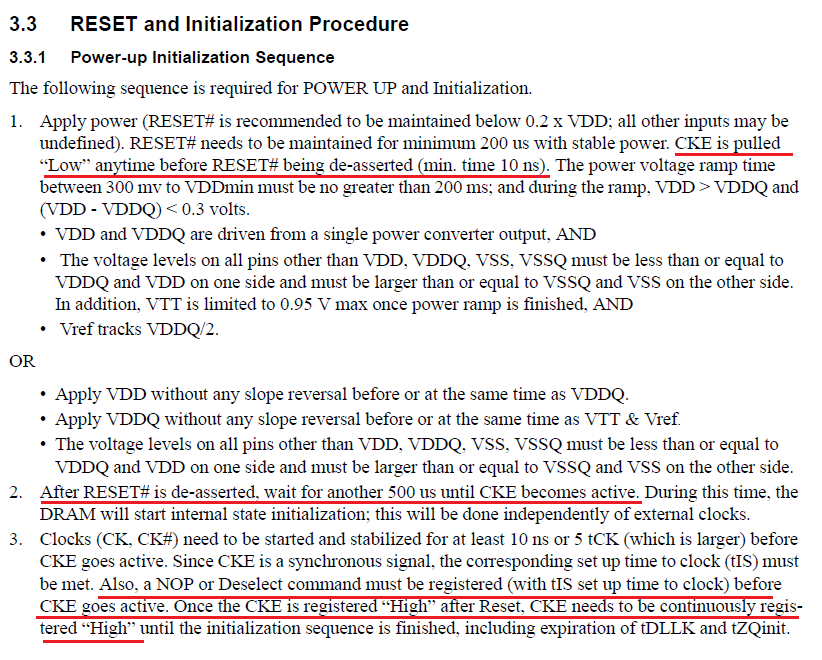

1.虽然 VDDQ 具有有效的电压电平、但我不认为 CKE 与 VDDQ 之间的短接始终有效。 根据 JEDEC DDR3规范、在上电时必须将 CKE 拉至低电平。

然后、在 RESET#取消置位后、您应该等待500us、直到 CKE 激活。 JEDEC DDR3规范的"3.3复位和初始化过程"部分对此进行了介绍。

以下摘录:

如果您只将 CKE 连接到 VDDQ、我无法评论会发生什么情况。 如果您幸运、SDRAM 可能会被成功访问。

如果您的电路板用于评估、您可以使用当前的"硬件补丁"、但我不建议将其用于最终产品。

此类权变措施可用于测试目的、或者如果您需要在不生产新电路板的情况下修复某些问题、但不得在供客户使用的产品中使用。

除了将 EMIF2 CKE 连接到 SDRAM CKE 引脚之外、任何其他方法都不是一种好的专业工程方法。 如果听起来有点粗鲁的话,很抱歉。 这不是目的。

此外、J6数据手册还指出、上电后 CKE 为低电平。

2.如果您在不使用 EMIF2 CKE 的情况下找到了遵循 JEDEC 的方法、我认为您也不应该隔离 EMIF1 CKE。 这不应影响交错。

3.如果您不使用自刷新、功耗将会更高、但我不期望有显著差异。 请注意、在这种情况下、EMIF_POWER_MANAGEMENT_CONTRAIN[10:8] LP_MODE 位字段应设置为值!= 0x2以禁用自刷新。

不使用自刷新的另一个影响是、您无法更改 EMIF_FICLK 频率、因为只有在将外部 SDRAM 置于自刷新模式后才能更改该频率。

BR、

Dobrin