大家好、

我将 OMAP-L138 与 C674x DSP 搭配使用。 McBSP 通过 FIFO 连接到 EDMA。 在正常操作下、我的应用程序工作正常、它将经常停止并启动 EDMA 和 McBSP。 串行端口配置为使用外部 FSX 和 CLKX。 一旦串行端口启动、锁定似乎总是发生、而不是在操作过程中、因此故障可能发生在先前关闭串行端口或重新初始化和启动故障发生时。

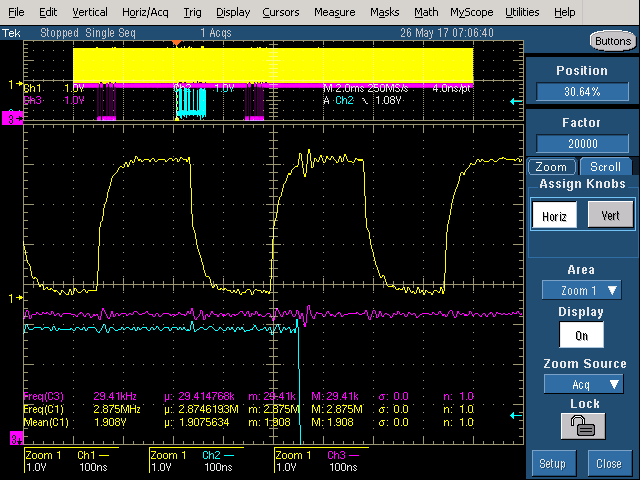

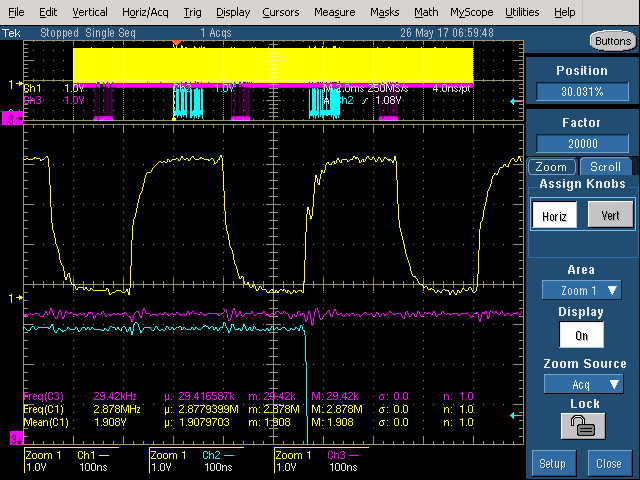

为了使锁定更频繁地发生、我已经为 McBSP 提供了一个过大的噪声时钟、并且观察到与最初锁定相同的症状(如下所述)。 我在提供时钟时有时不可靠的器件上遇到了问题(过去时钟消失时、我遇到了问题)。 我知道坏时钟是导致问题的原因、但我想更具体地了解这个问题是如何发生的以及症状是什么。 提供时钟的器件是第三方器件、因此它基本上是我的另一个黑盒。

发生锁定后、我已经对寄存器进行了调查、以了解可能出现的问题。 EDMA 没有 McBSP Tx 事件的中断挂起(IPR)、EMR 和 SER 都是清零的。 EDMA 指向第65个元素、该元素是要加载到 FIFO 中的下一个元素、它位于 EDMA 参数集的中间位置。 FIFO 似乎已满(长度64)。 Mcbsp0DSP.SPCR 为0x02032007 (McBSP 接收器正在使用中并且仍在运行)、显示:

- XRDY 为"1-是"

- XEMPTY 为'0-Yes'

- XRST 已启用

- XSYNCERR 为'0-no'。

- XINTM 为'00-XRDY'

我将此读作表示 McBSP 认为它已发送 DXR (已设置为 EDMA 传输的第一个元素)、因为它认为它是空的并已准备好在 DXR 中接收新数据。 作为仿真器中的实验、我切换了 XRST 以禁用并重新启用 McBSP。 我看到 DXR 更新到我预期的元素#2、XRDY 和 XEMPTY 处于与上面相同的状态。 FIFO 保持满、EDMA 增加了一个指向第66个元件的位置。 串行端口仍保持锁定在[现在]第二个元件上。 看起来整个"链"仍然正常工作、因此我怀疑问题不在 EDMA 或 FIFO 中。 我还对 DXR 引脚的活动进行了物理监控、看不到任何活动(常量为零)。 即使在切换 XRST 之后、我也看不到 DXR 引脚上没有任何活动(甚至没有单次传输)、即使我希望 McBSP 持续传输 DXR 的内容、即使它认为它有下溢(FREE ="1 - ENABLE")。

因此、这篇文章的第二部分是、我正在寻找一种从这种情况中恢复的方法。 执行软复位(重新加载 C674x 代码)不会恢复、下次启动串行端口时、会出现相同的症状。 DSP 应用的重新启动非常严格地遵循用户指南中的 McBSP 初始化过程。 我唯一找到的恢复方法是通过硬复位关闭整个模块。 在这种情况下、我尝试使用 PSC 禁用并重新启用 McBSP0、但不管我尝试转换到什么状态、pstat 都保持为'1-正在转换'、就好像它没有从 McBSP0接收任何类型的通信一样。 然后、如果我尝试读取任何 McBSP0寄存器、我的内核会挂起且调试终止、唯一的恢复是硬断电复位。

因此、我将寻找两个问题的答案:

1) 1)锁定到底是什么?它是如何进入此状态的?

2) 2)除关闭模块电源外、是否还有任何恢复机制?

感谢您的观看、

马歇尔