您好!

我对 C5517器件的 I2S2有疑问、我客户的电路板在不从 I2S2输出数据方面存在问题。

详细信息如下所示:

C5517是 I2S 主器件、它连接到从属微型计算机、如下所示。

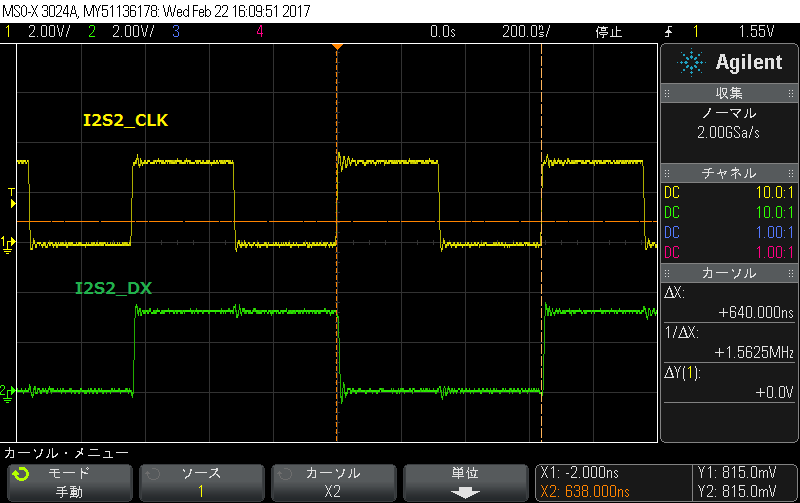

通常会输出 CLK 信号和帧同步、但每个 TX 数据都未正确输出、即使 CCS 将数据直接写入 TX 缓冲区、也会发生相同的现象。

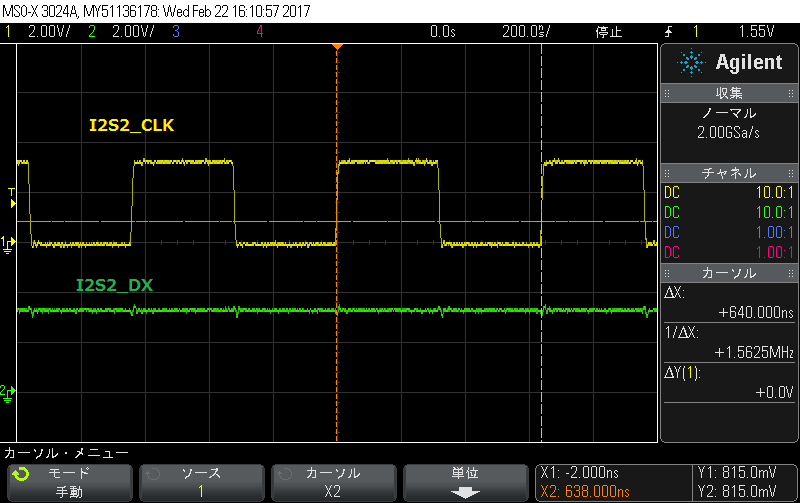

现已确认问题已通过以下方法解决。

方法1:

切断 I2S2_CLK 和测试端口之间的模式。

方法2:

将 I2S2SCTRL.DATADLY 位设置从1位数据延迟更改为2位。 或者、使用 DSP 格式而不是 I2S 格式。

当 C5517用作 I2S 主器件时、似乎存在一些限制。

特别是、C5517对 I2S 时钟线的图形长度和负载容量有限制吗?

此致、

H.U