工具/软件:Linux

大家好、

我们使用 DRA7xx_GLSDK_7.04.00.03开发定制板。

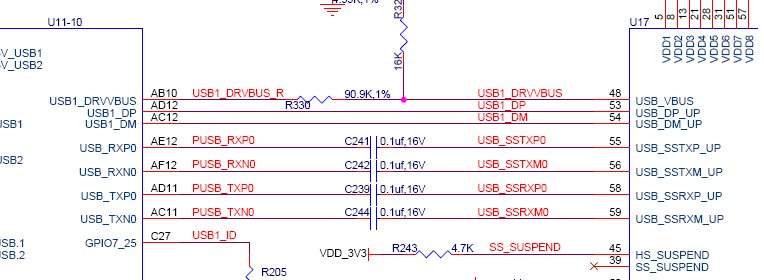

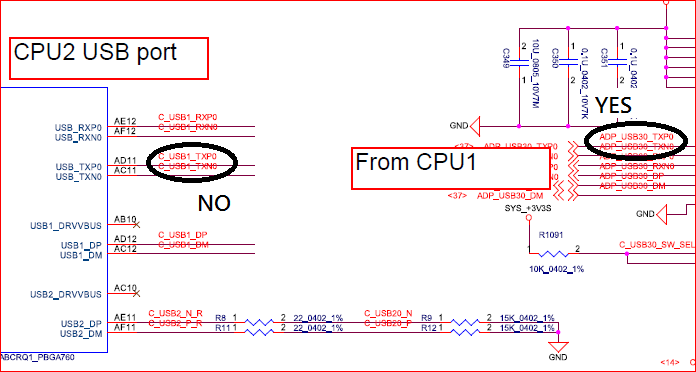

我们有两个使用 dra750作为 CPU 的定制板、并将其 USB1 (3.0端口)连接在一起。

一种是设置为主机模式、另一种是设置为器件模式。

当我们在器件1上移动探测器 g_mass 存储.ko 时、

主机将检测大容量存储:/dev/sda、

(请参阅 :processors.wiki.ti.com/.../Linux_Core_DWC3_User's_Guide)

然后、我们对/dev/sda 进行分区和格式化、并将其安装到目录中。

最后、我们使用 dd 命令在该目录中创建文件。

问题在于、它似乎在高速模式下运行、而不是在超高速模式下运行。

如何使其在超高速下工作或任何设置都可以强制两个 USB1端口在超高速下工作?

请给我一些建议、非常感谢。