您好 TI

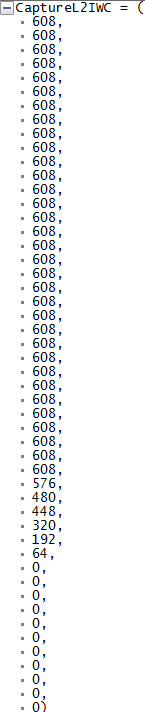

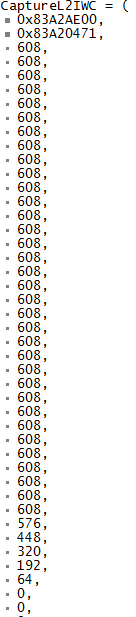

在外部存储器中、我有一个 EDMA 存储器从一个存储器位置传输到另一个存储器位置。 大小约为19 KB。 我使用缓存无效来确保刷新缓存、但测试显示部分存储器未刷新。

下面是我要做的:

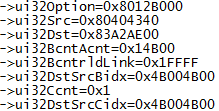

1) memset (&stDataFile[ui8DataFileIndex].stData、0、sizeof (stDataFile[ui8DataFileIndex].stData);

2) BCACHE_wbInv (&stDataFile[ui8DataFileIndex].stData、sizeof (&stDataFile[ui8DataFileIndex].stData)、true);

3) 3) Initaite EDMA 传输

4) 4)通过 检查 IprH 寄存器中的位等待 EDMA 传输完成

5) BCACHE_INv (&stDataFile[ui8DataFileIndex].stData、sizeof (stDataFile[ui8DataFileIndex].stData)、true);

如果我在步骤5之后检查数据、存储器中有值为0的随机范围(来自步骤1中的 memset)。

如果我等待几 ms (TSK_SLEEP)或更长时间、数据是正确的。

是否有任何可能导致这种情况的建议?