https://e2e.ti.com/support/processors-group/processors/f/processors-forum/600508/nor_flash_uboot

主题中讨论的其他器件:X5777AXGABC、 X5777BXGABC你(们)好

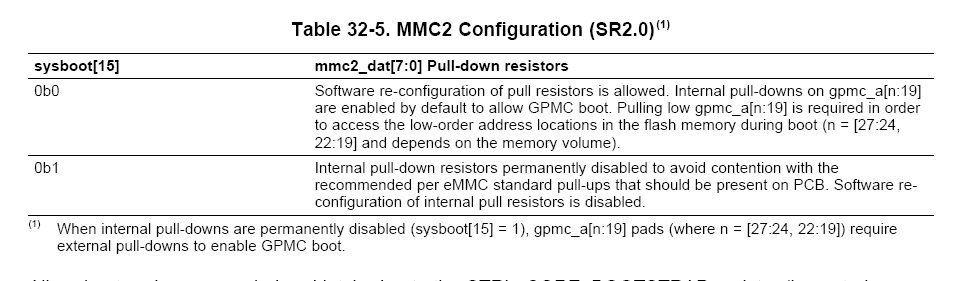

我们在处理器 X5777BXGABC (器件版本2.0)中遇到 NOR 闪存启动问题、它从 X5777AXGABC (器件版本1.1)迁移。

我们能够访问 NOR 闪存及其在 Silicon Revision2.0和 Silicon Revision 1.1中的数据 ,但它不是从 NOR 闪存引导的。

我们已经进行了配置设置、使其首先引导 MMC、如果 MMC 不可用、则应从 NOR 引导。