您好!

一段时间前 、C6678中的 PCIe 出站大小有类似的主题。 虽然该线程被标记为已解决、但我看不到它到底有多大帮助。 现在轮到我提出完全相同的问题了。

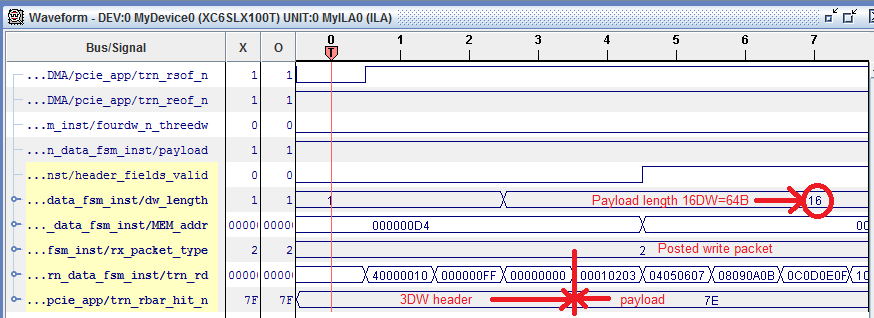

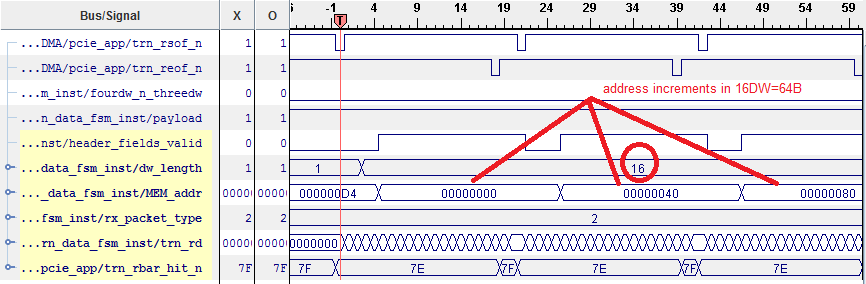

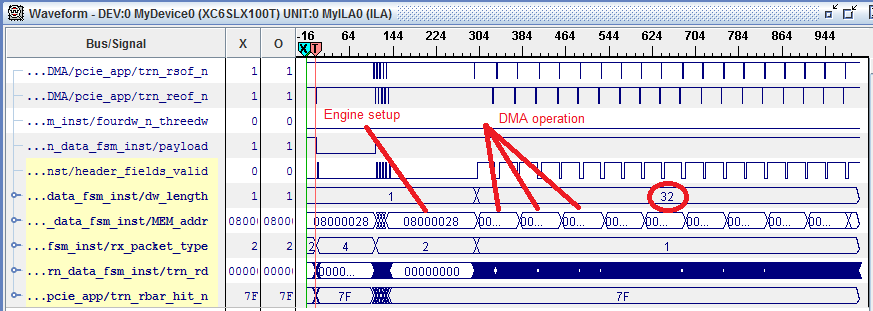

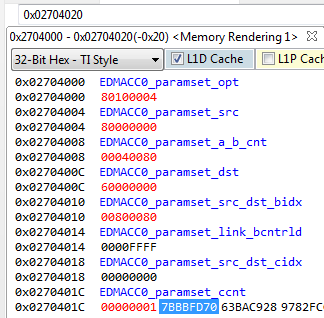

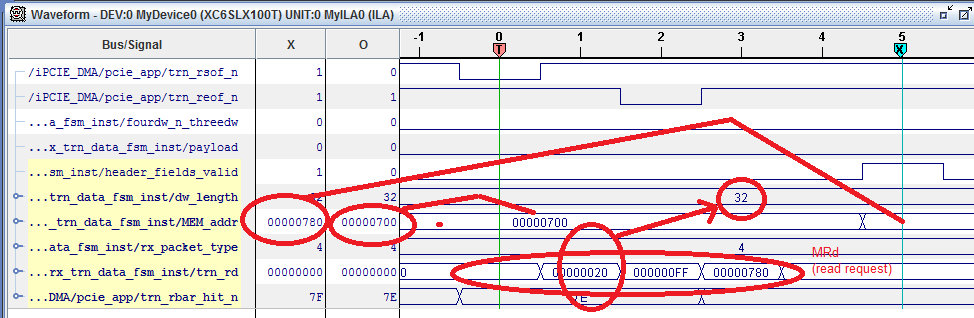

我有 C6670。 我将通过 EMDACC0设置 EDMA 传输、其两个传输控制器的 DBS 均为128B。 我将传输大小设置为2K。 我正在监控 EP 上的 PCIe 事务接口、即 FPGA。 我看到 TLP 的有效载荷大小为16 DWORD、即64B。 我还看到32次传输、因此每次传输2048B/32=64B。 此外、在 TLP 头中、我看到目标地址为0x0000、0x0040、0x0080、它们以64B 的倍数递增。

另一方面、我确信我的 FPGA 将 DEV_CAP_MAX_PAYLOAD_SUPPORTED 参数广播为128B。

因此、我要再次询问、如何通过 PCIe 使用 EDMA 实施128B 出站传输。

提前感谢。