http://www.ti.com/lit/ds/sprs957d/sprs957d.pdf 中 关于 PDN 实施指南的第8.4章规定:" TI 仅支持遵循 http://www.ti.com/lit/pdf/spraby8 应用报告中所含电路板设计指南的设计。

本报告介绍的是 AM572x MPU、而不是 AM571x MPU。 不是一个大问题、但更重要的问题是表2中有关去耦电容器的建议。

| 电压 | 100nF | 220nF | 470nF | 1 μ F | 2.2 μ F | 4.7 μ F | 22 μ F |

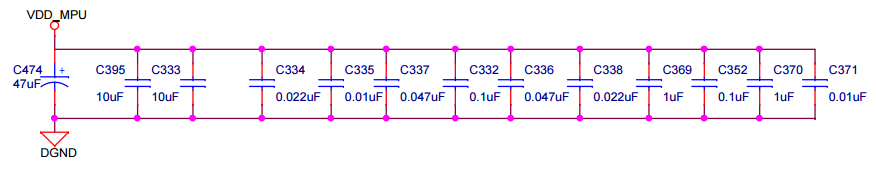

| VDD_MPU | 12. | 2. | 2. | 3. | 1 | 1 | 1 |

这些建议与 http://processors.wiki.ti.com/index.php/General_hardware_design/BGA_PCB_design/BGA_decoupling 上 的建议不完全一致,该建议指出:

"基于电容器的值通常不同、造成的伤害比良好的伤害更大(由于上面列出的谐振可能性)、 而对于较新的电容电介质、较大值的电容具有几乎相同的高频阻抗、与相同尺寸的较小电容值相同。我们建议在贵公司可制造的最小封装中仅使用一个值0.1uF-0.2uF (这应该是0402大小或更小)。 "

还是将大于100nF 的电容器视为大容量电容器?

无论如何、值得注意的是、AM5718参考设计(http://www.ti.com/lit/df/sprr242/sprr242.pdf)肯定不会遵循上述 建议。

TI 内部的不同学校?

此致

/F