主题中讨论的其他器件: AM3352

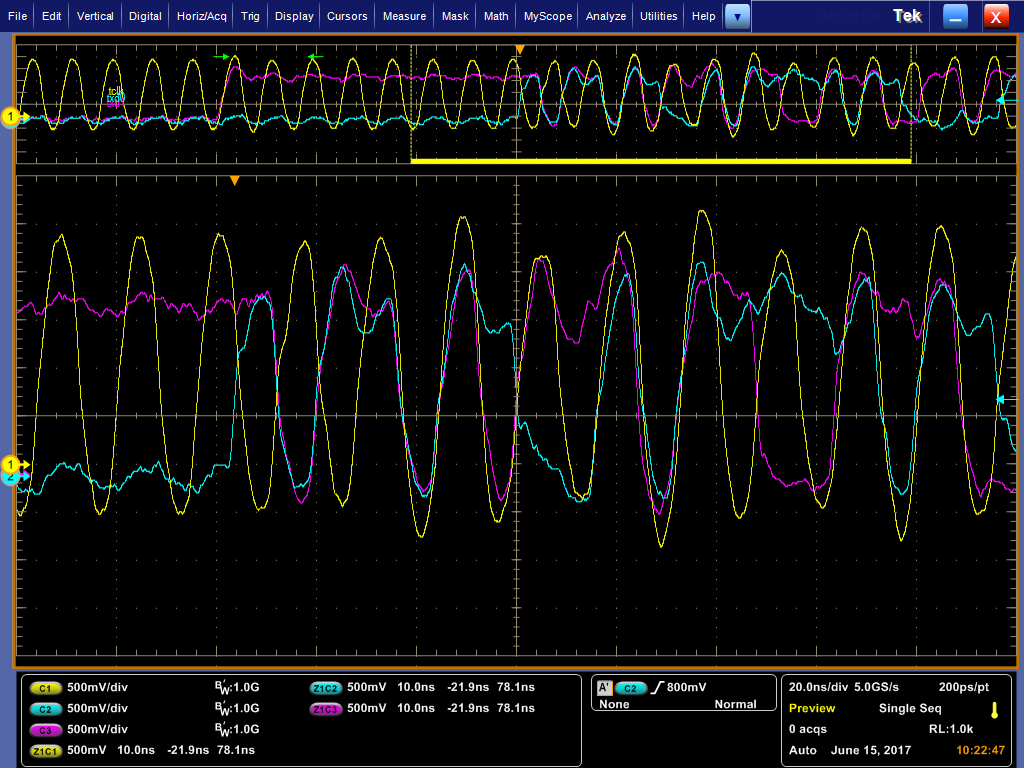

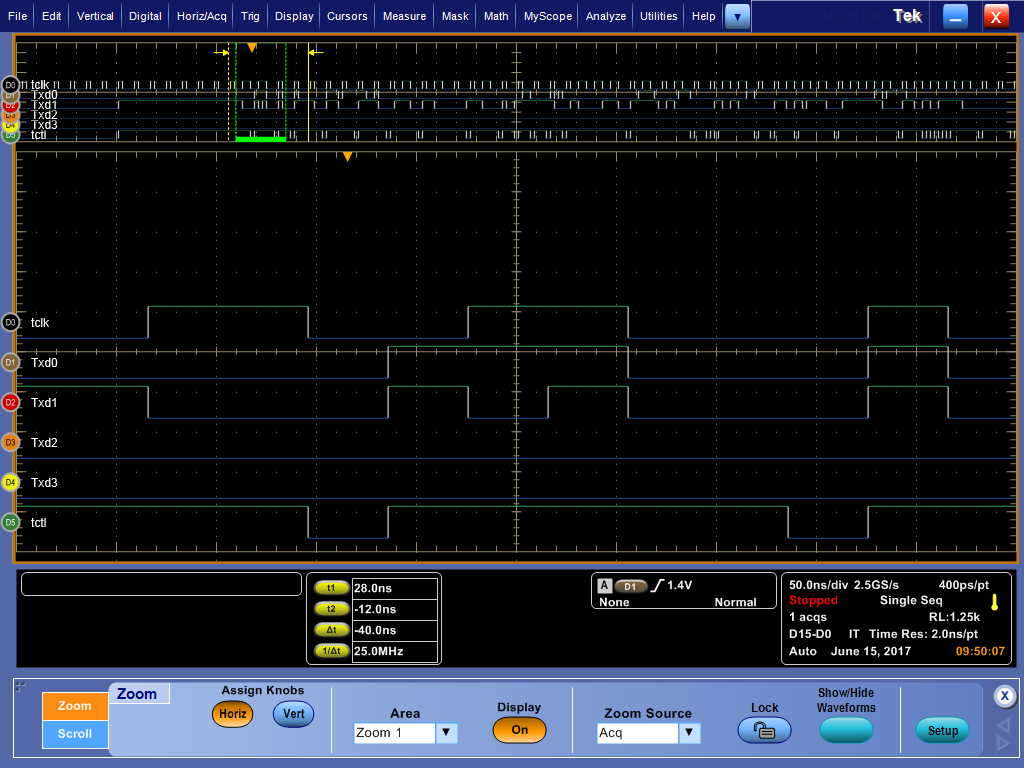

我正在进行基于 AM3358的设计。 一段时间以来,我们一直在努力使千兆位以太网正常工作,但没有任何运气。 我们使用 Microchip’s/Micrel’s KSZ9031RNX PHY,它通过 RGMII 与 AM3358进行通信。 当我们使用1 Gb 链路进行吞吐量测试时、通常只能看到~1 Mbps。 使用10/100链路,我们可以看到速度符合我们的预期。 我们认为、我们的偏斜值会出现问题、从而导致千兆位速度出现问题。

尽管在电路板布局和组装之前在数据表中找到这一点很有帮助、但我们发现 TI 论坛文章建议接收和发送时钟延迟1.8ns; 这篇文章使用的是 AM3352 (而不是 AM3358)、但使用的是与我们相同的 PHY。

https://e2e.ti.com/support/arm/sitara_arm/f/791/p/334206/1166129

考虑到该目标、我们修改了 PHY 偏斜寄存器、使其尽可能接近、同时考虑到电路板上的实际布线长度(请参阅下面的电子表格)。 在接收端(从处理器的角度看输入)、PHY 在接收时钟垫上已经有1.2ns 的默认延迟。 因此、我们(通过寄存器)添加了0.6ns 延迟、以达到建议的1.8ns。 在发送端,没有默认延迟,因此我们必须调整时钟、数据和控制线的偏差(时钟偏差+,数据和控制偏差)。 由于两个方向上的最大延迟、我们只能使用寄存器达到1380ps、因此我们必须在电路板上的时钟信号中添加~420ps。 这采用了3.1英寸导线的形式,该导线已添加到电路板上,如下所示。

即使发生了这些变化、我们仍会看到在传输方向上重试的次数很多。 接收路径不存在此问题。

应用工程师能否:

- 确认1.8ns 延迟是建议的延迟。

- 建议调试此问题的后续步骤。

谢谢!

Matt