工具/软件:Linux

你(们)好

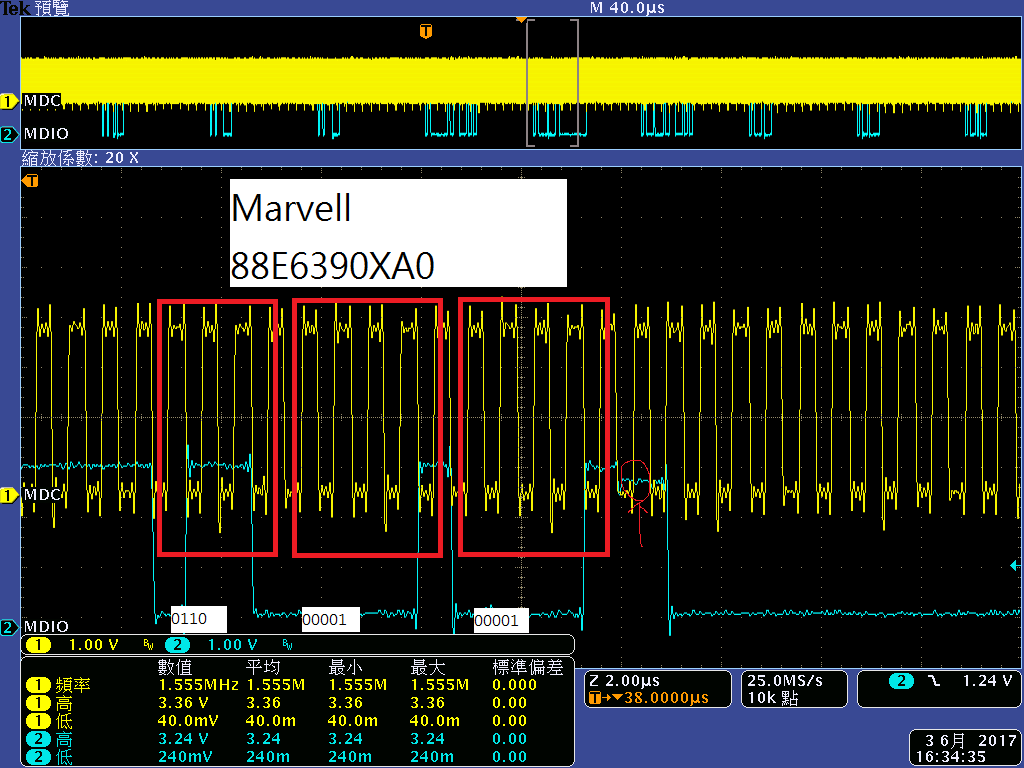

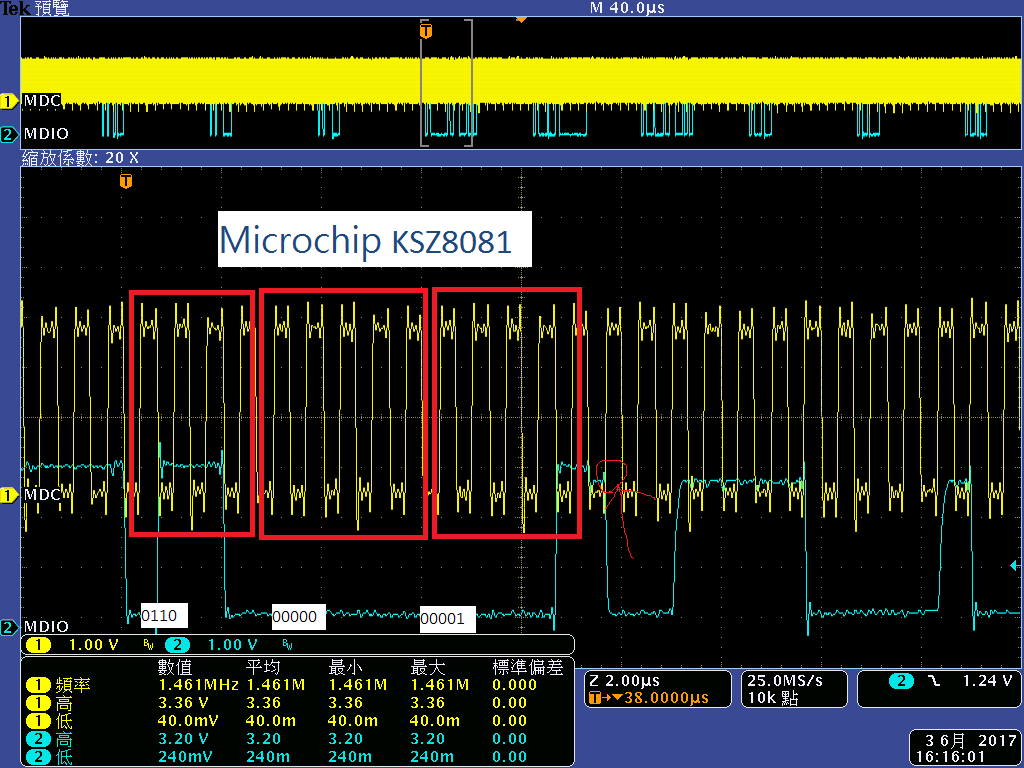

我将两个以太网设备 Microchip KSZ8081和 Marvell 88E6390XA0与 DRA744的 MDIO/MDC 连接在一起。

我可以 通过 MDIO 读取命令获取 KSZ8081器件信息、但 88E6390XA0仅返回错误。

我们还致电 Marvell FAE 帮助、FAE 可以通过其固定工具获取88E6390XA0器件信息。

然后、我尝试测量该波形、找出 KSZ8081 和 88E6390XA0之间的差异。

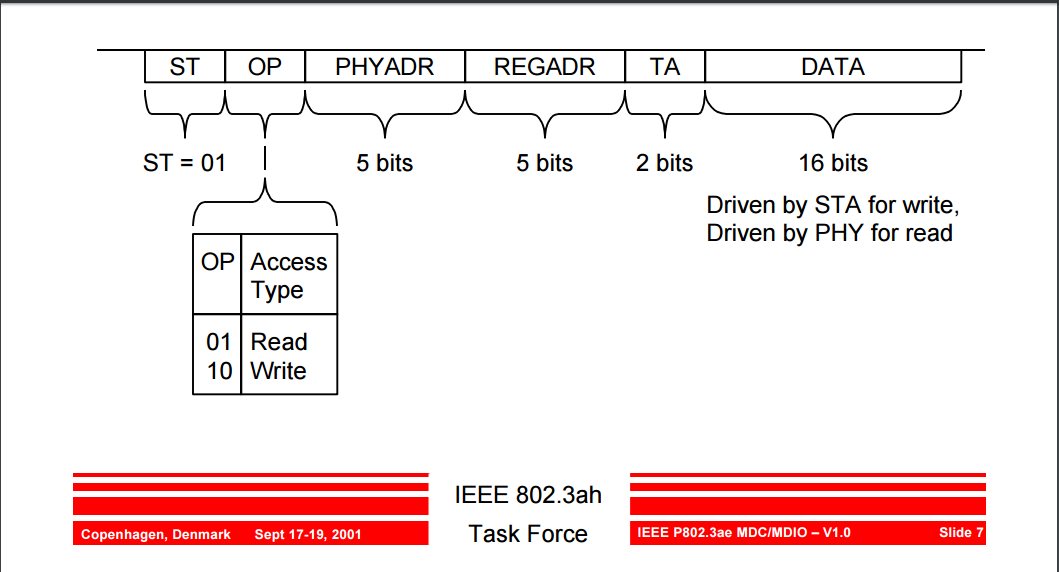

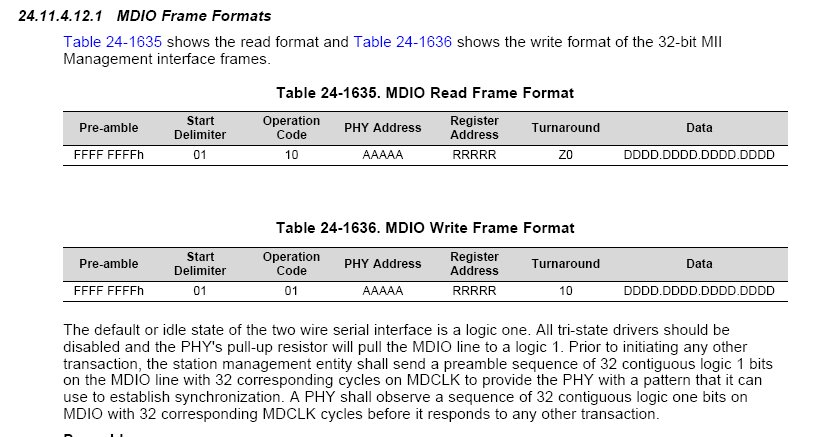

在 DRA744被发送寄存器地址后、 88E6390XA0有一个额外的高电平位。 如下图所示。

是否有任何寄存器设置可以覆盖此差异?

谢谢你