主题中讨论的其他器件: CDCE62005

您好!

我根据 TMDSEVM6657制作了自己的电路板。

我的电路板不完全相同 、但基本上与 TMDSEVM6657相同。

我在 DSP 和 CDCE62005之间遇到了问题。

它们之间的引脚映射 如下所示。

CDCD62005 DSP

CH0 -> SRIOSGMICLK:250MHz

CH1 -> 未使用

CH2 -> DDRCLK:66MHz

CH3 -> CORRECLK:100MHz

CH4 -> 未使用

我添加了一个端口、用于 通过 SPI 引脚直接与 CDCE62005通信。

该端口仅用于对 CDCE62005进行编程。

通常 、CDCE62005的 SPI 引脚 连接到 FPGA。

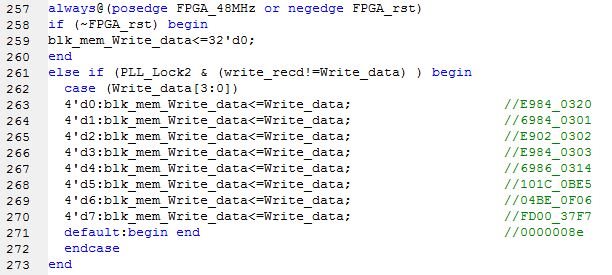

CDCE62005的配置如下所示。

该值是从 EVM FPGA 代码复制的。

0: 0xE9840320

1:0x69840301

2: 0xE9020302

3:0xE9840303

4:0x69860314

5:0x101C0BE5

6:0x04BE0F06

7: 0xFD0037F7

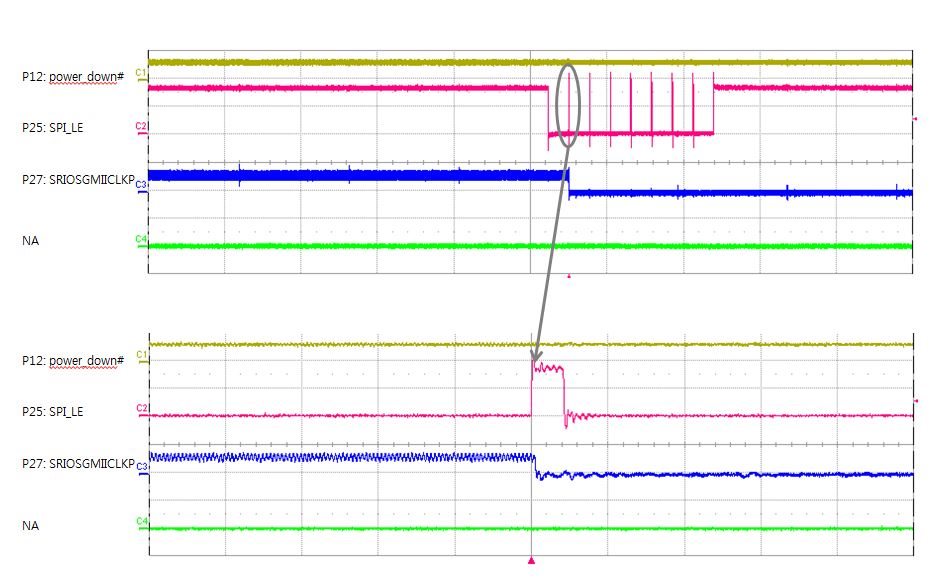

使用 EVM FPGA 代码启动电路板后 ,我可以看到一个正弦波只来自 CDCE62005的 CH2、CH3。

对于 ch0、我也可以从它看到正弦波、但它的时间非常短。

此 FPGA 代码与 EVM 不完全相同。

随附部分代码、名为"modificaite.zip"。

如果我使用 FPGA 代码、 我可以看到 来自 ch0、ch2和 ch3的正弦波。

此代码与"modificaite.zip"不同。

请查看随附的"my_code.zip"文件。

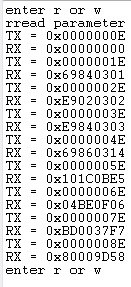

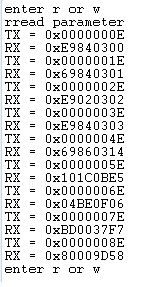

此代码非常简单、只需在外部 端口和 CDCE62005 SPI 引脚之间建立连接即可。

使用此代码、我可以通过 SPI 访问 CDCE62005的寄存器。

从 寄存器中、我确认 PLL 已锁定。

如果我再问一次、CDCE62005的输出 在哪种情况下会关闭。

此致

Yun-Seok Cho

e2e.ti.com/.../my_5F00_code.zip

e2e.ti.com/.../modification.zip